### 1

# **Fabrication Technology**

O. Brand, School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA, USA

#### Abstract

This chapter provides an overview on fabrication technologies for CMOS-based microelectromechanical systems (MEMS). The first part briefly introduces the basic microfabrication steps, highlights a CMOS process sequence and how CMOS materials can be used for microsystems design. While a number of microsystems can be fabricated within the regular CMOS process sequence, the focus of the chapter is on combining CMOS technology with micromachining process modules. CMOS-compatible bulk and surface micromachining techniques are introduced in the second part of the chapter together with an overview of the design challenges faced when combining mechanical microstructures and electronics on the same substrate. The micromachining modules can either precede (pre-CMOS), follow (post-CMOS) or be performed in between (intra-CMOS) the regular CMOS process steps. The last part of the chapter provides an extensive overview on the different CMOS-based MEMS approaches found in the literature.

#### **Keywords**

Micromachining; CMOS-based MEMS; MEMS fabrication; microsystem fabrication

| 1.1     | CMOS Technology 2            |   |

|---------|------------------------------|---|

| 1.1.1   | Basic Microfabrication Steps | 4 |

| 1.1.1.1 | Thin Film Deposition 5       |   |

| 1.1.1.2 | Patterning 6                 |   |

| 1.1.1.3 | Etching 8                    |   |

| 1.1.1.4 | Doping 9                     |   |

Advanced Micro and Nanosystems. Vol. 2. CMOS – MEMS. Edited by H. Baltes, O. Brand, G. K. Fedder, C. Hierold, J. Korvink, O. Tabata Copyright © 2005 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim ISBN: 3-527-31080-0

| 1.1.2   | CMOS Process Sequence 9                           |

|---------|---------------------------------------------------|

| 1.1.3   | CMOS Materials for Micro- and Nanosystems 11      |

| 1.1.4   | CMOS Microsystems 14                              |

| 1.2     | CMOS-compatible Micromachining Process Modules 17 |

| 1.2.1   | Bulk Micromachining 18                            |

| 1.2.2   | Surface Micromachining 22                         |

| 1.3     | CMOS-compatible Design of MEMS and NEMS 23        |

| 1.3.1   | Tolerable Process Modifications 24                |

| 1.3.2   | Design Rule Modifications 26                      |

| 1.3.3   | Simulation of Circuitry and MEMS 27               |

| 1.4     | CMOS and Micromachining 28                        |

| 1.4.1   | Pre-CMOS Micromachining 33                        |

| 1.4.2   | Intra-CMOS Micromachining 37                      |

| 1.4.3   | Post-CMOS Micromachining 43                       |

| 1.4.3.1 | Post-CMOS Micromachining of Add-on Layers 43      |

| 1.4.3.2 | Post-CMOS Micromachining of CMOS Layers 49        |

| 1.5     | Conclusion 56                                     |

| 1.6     | References 57                                     |

# 1.1 CMOS Technology

State-of-the-art CMOS processes, such as IBM's 9S2 process based on SOI (silicon-on-insulator) technology on 300 mm wafers, feature a minimal physical gate length of less than 100 nm and up to eight (copper) metallization levels (see Fig. 1.1, [1]). Such advanced CMOS processes are required for the fabrication of today's and tomorrow's microprocessors comprising tens of millions of transistors on a single chip. An example is Apple Computer's 64-bit PowerPC-G5 processor with more than 58 million transistors [2], manufactured using IBM's 90 nm CMOS technology.

Researchers at IBM's T.J. Watson Research Center have recently used the copper-based interconnect technology of such modern CMOS processes to fabricate microelectromechanical devices, namely r.f. switches and resonators [3, 4]. Up to now, however, most commercially available microsystems combining (micromachined) transducer elements and integrated electronics on a single chip rely on CMOS or BiCMOS processes with minimum feature sizes typically between 0.5 and 3  $\mu$ m and 4 or 6 in wafer sizes. While the underlying CMOS technologies are between 10 and 15 years old, their capabilities are sufficient for most microsystem applications. An example is the pressure sensor KP100 by Infineon Technologies, a surface micromachined pressure sensor array with on-chip circuitry for signal conditioning, A/D conversion, calibration and system diagnostic, which is based on a 0.8  $\mu$ m BiCMOS technology on 6 in wafers [5].

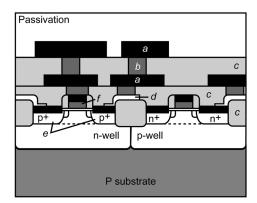

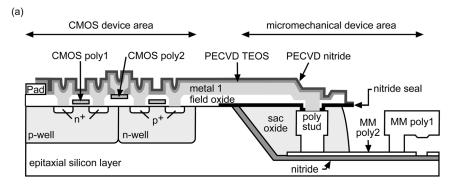

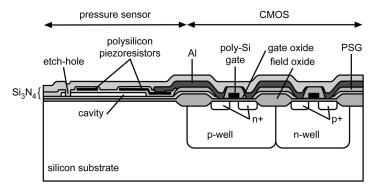

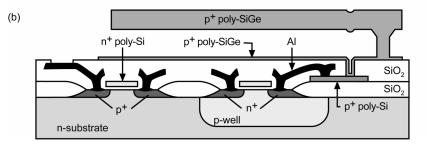

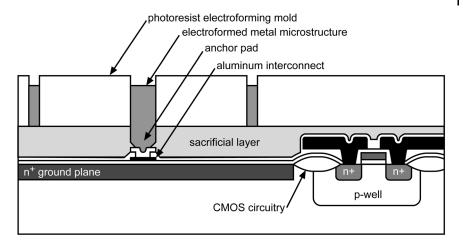

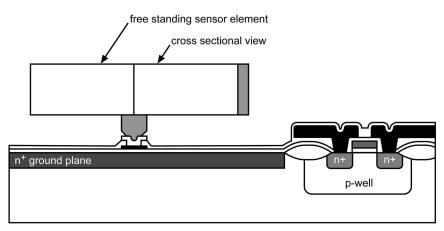

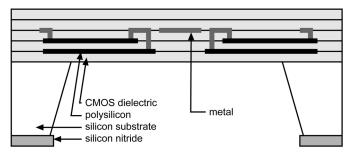

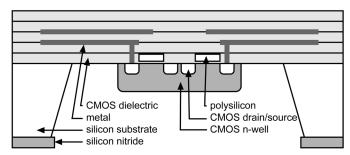

A typical cross-section of a sub- $\mu$ m (0.5–1.0  $\mu$ m) CMOS technology used for CMOS-based microelectromechanical systems (MEMS) is shown in Fig. 1.2 [6].

<u>0.5 μm</u>

Fig. 1.1 Cross-section of IBM's 90 nm CMOS technology 9S2 with 8-level copper metallization (labeled M1–M8) with close-up of three metal–oxide–semiconductor field effect tran-

sistors (MOSFETs). Images courtesy of International Business Machines Corporation; unauthorized use not permitted

- a Aluminum metallization

- b Tungsten via

- c Oxide

- d TiN local interconnect

- e LDD source/drain

- f Polysilicon gate

Fig. 1.2 Schematic cross-section of typical sub- $\mu$ m (0.5–1.0  $\mu$ m) CMOS technology with two-level aluminum metallization and TiN local interconnects. Adapted from [6]

The twin-well technology is based on 6 in p-type wafers and uses a polysilicon/silicide gate, low-doped drain (LDD) technology for source and drain formation, silicide source/drain contacts and a two-level metallization based on tungsten plugs and aluminum interconnects. A thermal oxide separates adjacent transistors, chemical vapor deposition (CVD) silicon dioxide layers are used as dielectric layers between the metallization levels and a PECVD (plasma enhanced CVD) silicon nitride layer or a silicon dioxide, silicon nitride sandwich are employed as pas-

sivation layer. The CMOS fabrication sequence is briefly highlighted in Section 1.1.2. More detailed process descriptions can be found in a number of microelectronics textbooks, e.g. [6–8].

When designing CMOS-based MEMS or microsystems, the designer must adhere, to a great extent, to the chosen CMOS process sequence in order not to sacrifice the functionality of the on-chip electronics. This limits the available 'design space' for the integrated microsystems, as e.g. materials, material properties and layer thicknesses are determined by the CMOS process. In the following, a brief introduction into integrated circuit fabrication will be given: the basic fabrication steps are highlighted (Section 1.1.1) and a CMOS process sequence is summarized (Section 1.1.2). Section 1.1.3 discusses how the different CMOS materials and layers can be used in micro- and nanosystems and Section 1.1.4 depicts a few microsystems that can be completely formed within a regular CMOS sequence.

# 1.1.1 Basic Microfabrication Steps

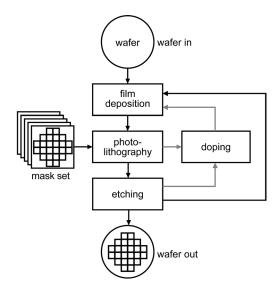

The fabrication of integrated circuits (ICs) using CMOS or BiCMOS technology is based on four basic microfabrication techniques: deposition, patterning, doping and etching. Fig. 1.3 illustrates how these techniques are combined to build up an IC layer by layer: a thin film, such as an insulating silicon dioxide film, is deposited on the substrate, a silicon wafer. A light-sensitive photoresist layer is then deposited on top and patterned using photolithography. Finally, the pattern is transferred from the photoresist layer to the silicon dioxide layer by an etching process. After removing the remaining photoresist, the next layer is deposited and struc-

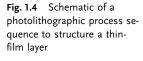

Fig. 1.3 Flow diagram of IC fabrication process using the four basic microfabrication techniques: deposition, photolithography, etching and doping. Adapted from [8]

tured, and so on. Doping of a semiconductor material by ion implantation, the key step for the fabrication of diodes and transistors, can be performed directly after photolithography, i.e. using a photoresist layer as mask, or after patterning an implantation mask (e.g. a silicon dioxide layer).

Silicon is the standard substrate material for IC fabrication and, hence, the most common substrate material in microfabrication in general. It is supplied as single-crystal wafers with diameters between 100 and 300 mm. In addition to its favorable electrical properties, single-crystal silicon also has excellent mechanical properties [9], which enable the design of micromechanical structures. CMOS processes for digital electronics typically use low-doped (doping concentration in the 10<sup>16</sup> cm<sup>-3</sup> range) silicon wafers, whereas processes for mixed-signal or analog electronics are often based on high-doped (doping concentration in the 10<sup>19</sup> cm<sup>-3</sup> range) wafers with a low-doped epitaxial layer to minimize latch-up. The choice of the substrate material might already require a compromise between the requirements for the MEMS part and the on-chip electronics: the fabrication of membrane structures for, e.g., pressure sensors is typically based on anisotropic silicon etching in a potassium hydroxide (KOH) solution (see Section 1.2). High p-type doping  $(N_A \ge 10^{19} \text{ cm}^{-3})$  substantially reduces the silicon etch rates in KOH solutions, thus preventing the use of highly p-doped CMOS substrates in combination with KOH etching.

In the following, a brief overview on the four basic microfabrication steps will be given. More details can be found in textbooks and reference books on semiconductor processing [6–8, 10, 11].

#### 1.1.1.1 Thin-film Deposition

The two most common thin-film deposition methods in microfabrication are chemical vapor deposition (CVD), performed at low pressure (LPCVD), atmospheric pressure (APCVD) or plasma-enhanced (PECVD), and physical vapor deposition (PVD), such as sputtering and evaporating. Typical CVD and PVD film thicknesses are in the range of tenths of nanometers up to a few micrometers. Other film deposition techniques include electroplating of metal films (e.g. the copper metallization in state-of-the-art CMOS processes) and spin- or spray-coating of polymeric films such as photoresist. Both processes can yield film thicknesses from less than 1 µm up to several hundreds of micrometers.

Dielectric layers, predominantly silicon dioxide, SiO2, and silicon nitride, SiNx, are used as insulating material, as mask material and for device passivation. Silicon dioxide is either thermally grown on top of a silicon surface (thermal oxide) at high temperatures (900-1200 °C) in an oxidation furnace or it is deposited in a CVD system (CVD oxide). CVD oxides can be deposited at temperatures between 300 and 900 °C, with the high-temperature depositions usually yielding better film properties. Low-temperature CVD oxide films are typically deposited in PECVD systems and high-temperature CVD oxide films in LPCVD equipment. Silicon nitride layers deposited in LPCVD furnaces are commonly used as masking

material during local oxidation of silicon (LOCOS process), while PECVD silicon nitride films are used for e.g. device passivation.

Highly doped polycrystalline silicon (polysilicon) is used as gate material for metal oxide semiconductor field effect transistors (MOSFETs), as electrode and resistor materials, for piezoresistive sensing structures, as thermoelectric material, and for thermistors. Polysilicon microstructures released by sacrificial layer etching are also widely used in sensor applications (see Section 1.4). Polysilicon is usually deposited in an LPCVD furnace using silane (SiH<sub>4</sub>) as gaseous precursor.

Metal layers are used, e.g., for electrical interconnects, as electrode material, for resistive temperature sensors (thermistors) or as mirror surfaces. Metals, which are widely used in the microelectronics industry, such as aluminum, titanium and tungsten, are routinely deposited by sputtering. Depending on the application, a large number of other metals, including gold, palladium, platinum, silver or alloys, can be deposited with PVD methods. A number of metals and metal compounds, such as Cu, WSi2, TiSi2, TiN and W, can be deposited by CVD. Metal CVD processes are less common, but can provide improved step coverage or local deposition of metals. Whereas aluminum has been the standard metallization in IC fabrication for many years, the state-of-the-art sub-0.25 μm CMOS technologies often feature copper as interconnect material, owing to its lower resistivity and higher electromigration resistance as compared with aluminum. An example is IBM's interconnect metallizations based on the so-called damascene process [12], which employ copper films electroplated in a dielectric mold. After each metallization step, planarization is achieved with a chemical-mechanical polishing (CMP) step.

Polymers such as photoresist are commonly deposited by spin- or spray-coating. Polymers can be used as dielectric materials, passivation layers, and as chemically sensitive layers for chemical and biosensors ([13]; see also Chapter 7).

### 1.1.1.2 Patterning

Photolithography is the standard process to transfer a pattern, which has been designed with computer-aided-engineering (CAE) software packages, on to a certain material. The process sequence is illustrated in Fig. 1.4. A mask with the desired pattern is created. The mask is a glass plate with a patterned opaque layer (typically chromium) on the surface. Electron-beam lithography is used to write the mask pattern from the CAE data. In the photolithographic process, a photoresist layer (photostructurable polymer) is spin-coated on to the material to be patterned. Next, the photoresist layer is exposed to ultraviolet (UV) light through the mask. This step is done in a mask aligner, in which mask and wafer are aligned with each other before the subsequent exposure step is performed. Depending on the mask aligner generation, mask and substrate are brought in contact or close proximity (contact and proximity printing) or the image of the mask is projected (projection printing) on to the photoresist-coated substrate. Depending on whether positive or negative photoresist was used, the exposed or the unexposed photoresist areas, respectively, are removed during the resist development process.

The remaining photoresist acts as a protective mask during the subsequent etching process, which transfers the pattern onto the underlying material. Alternatively, the patterned photoresist can be used as a mask for a subsequent ion implantation. After the etching or ion implantation step, the remaining photoresist is removed, and the next layer can be deposited and patterned.

The so-called *lift-off technique* is used to structure a thin-film material, which would be difficult to etch. Here, the thin-film material is deposited on top of the patterned photoresist layer. In order to avoid a continuous film, the thickness of the deposited film must be less than the resist thickness. By removing the underneath photoresist, the thin-film material on top is also removed by 'lifting it off', leaving a structured thin film on the substrate.

Thick photostructurable polymer layers, such as SU-8 [14], can be used as a mold for electroplating metal structures. A thick polymer layer is deposited on top of a metallic seed layer and photostructured. During the subsequent electroplating process, the metal is only deposited in the areas where the seed layer is exposed to the plating solution, i.e. the polymer layer acts as a plating mold.

Recently, microcontact printing or soft lithography [15] has been introduced as an additional method for pattern transfer. A soft polymeric stamp is used to reproduce a desired pattern directly on a substrate. Routinely, feature sizes on the order of 1  $\mu$ m can be achieved with this technique. The polymer stamp, often made from poly(dimethylsiloxane) (PDMS), is formed by a molding process using a master fabricated with conventional microfabrication techniques. After 'inking' the stamp with the material to be printed, the stamp is brought in contact with the substrate material, and the pattern of the stamp is reproduced. Surface proper-

ties of the substrate can therefore be modified to, e.g., locally promote or prevent molecule adhesion. Soft lithography has been specifically developed for biological applications such as patterning cells or proteins with the help of, e.g., self-assembled monolayers (SAMs) [15].

### 1.1.1.3 **Etching**

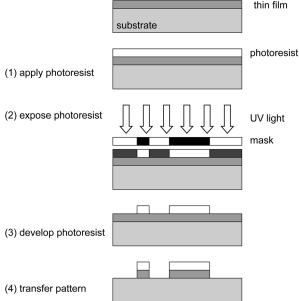

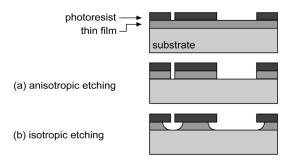

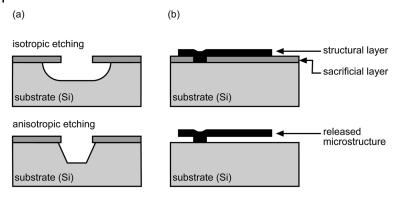

The two different categories of etching processes include wet etching using liquid chemicals and dry etching using gas-phase chemistry. Both methods can be either isotropic, i.e. provide the same etch rate in all directions, or anisotropic, i.e. provide different etch rates in different directions (see Fig. 1.5). The important criteria for selecting a particular etching process encompass the material etch rate, the selectivity for the material to be etched, and the isotropy/anisotropy of the etching process. An overview on various etching chemistries used in microfabrication can be found in [16].

Wet etching is usually isotropic with the important exception of anisotropic silicon wet etching in, e.g., alkaline solutions, such as potassium hydroxide (see Section 1.2). Moreover, wet etching typically provides a better etch selectivity for the material to be etched in comparison with neighboring other materials. An example includes wet etching of silicon dioxide using hydrofluoric acid-based chemistries.  $SiO_2$  is isotropically etched in dilute hydrofluoric acid (HF–H<sub>2</sub>O) or buffered oxide etch, BOE (HF–NH<sub>4</sub>F). Typical etch rates for high-quality (thermally grown) silicon dioxide films are  $0.1 \,\mu m/min$  in BOE.

Dry etching, on the other hand, is often anisotropic, resulting in a better pattern transfer, as mask underetching is avoided (see Fig. 1.5). Therefore, anisotropic dry etching processes, such as *reactive ion etching* (RIE), of thin-film materials are very common in the microelectronics industry. In an RIE system, reactive ions are generated in a plasma and are accelerated towards the surface to be etched, thus providing directional etching characteristics. Higher ion energies typically result in more anisotropic etching characteristics, but also in reduced etching selectivity.

Fig. 1.5 Schematic of isotropic and anisotropic thin-film etching

# 1.1.1.4 **Doping**

Doping is used to modify the electrical conductivity of semiconducting materials such as silicon or gallium arsenide. It is hence the key process step for fabricating semiconductor devices such as diodes and transistors. In the case of silicon, doping with phosphorus or arsenic yields n-type silicon, whereas p-type silicon results from boron doping. By varying the dopant concentration of n-type silicon from 10<sup>14</sup> to 10<sup>20</sup> cm<sup>-3</sup>, the resistivity at room temperature can be tuned from approximately 40 to  $7 \times 10^{-4} \Omega$  cm.

Dopant atoms are introduced by either ion implantation or diffusion from a gaseous, liquid or solid source. Ion implantation has become the key process to introduce precisely defined quantities of dopants in the microelectronics industry. The substrate material, i.e. a silicon wafer, is bombarded with accelerated ionized dopant atoms in an ion implanter. The result is approximately a Gaussian distribution of the dopant atoms in the substrate wafer with a mean penetration depth controlled by the acceleration voltage. A high-temperature diffusion process can then be used to additionally 'drive-in' the dopant until a desired doping profile has been achieved.

#### 1.1.2

#### **CMOS Process Sequence**

To be able to integrate microelectromechanical devices with CMOS circuitry, the designer must have an excellent understanding of the underlying CMOS process sequence. The particular process flow is, of course, strongly dependent on the chosen CMOS technology and a detailed description of a CMOS technology goes way beyond the scope of this chapter. Nevertheless, we briefly summarize a typical CMOS process sequence in the following, highlighting the main process steps and their importance for co-integration of CMOS and MEMS. We thereby follow the CMOS process sequence described in detail in [6] (see schematic cross-section in Fig. 1.2), which is typical for a sub-µm technology with minimal feature sizes between 0.5 and 1 µm.

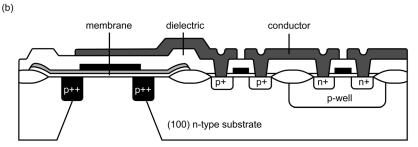

The starting wafer material is a lightly p-doped (100) wafer with a typical doping concentration of  $N_A \approx 10^{15} \text{ cm}^{-3}$ . The first step is the definition of the active areas by local oxidation of silicon (LOCOS), thus growing a thick ( $\sim 0.5 \, \mu m$ ) field oxide in the areas between the individual transistors. Next, the p-wells for the nchannel MOSFETs and the n-wells for the p-channel MOSFETs are implanted. A joint drive-in for both wells establishes the desired junction depth of 2-3 μm. Typical drive-in times are 4-6 h at 1000-1100 °C. We will see later (Section 1.2) that the n-well diffused in the p-substrate can be used to define accurately the thickness of a silicon membrane. Such membranes are commonly released by anisotropic wet etching from the back of the wafer using an electrochemical etch-stop technique at the p-n junction between n-well and p-substrate [17, 18].

After n- and p-well formation, the MOSFET gate and channel regions are engineered. First, channel implants for the n- and the p-channel transistors are implanted to adjust their threshold voltages to the desired values. After removing the implantation oxides in the active area, the gate oxide with a thickness ≤10 nm in modern CMOS processes is thermally grown in the active areas. Next, a 0.3-0.5 µm thick polysilicon layer for the gate electrodes is deposited across the wafer in an LPCVD furnace operating at about 600 °C and doped by ion implantation. Finally, the polysilicon layer is patterned to define the actual gate regions. In MEMS, the gate polysilicon can also be used for resistors, piezoresistors, thermopiles, electrodes and as structural materials. The last application often requires a high-temperature anneal of the polysilicon to reduce its residual stress to values acceptable for the microstructures. Such a high-temperature step can be critical at this stage in the CMOS process, as it might effect previous doping distributions and, hence, the CMOS device characteristics.

After gate formation, the source/drain regions are implanted. In typical sub-µm CMOS technologies, this is done using a LDD (lightly doped drain) process. It provides a gradient in the doping of the source/drain regions towards the channel region, reducing the peak value of the electric field close to a channel and, hence, increasing device reliability. First, phosphorus (or arsenic as alternative n-type dopant) is implanted in the source/drain of the NMOS transistors to form n regions, followed by a boron implantation of the source/drain of the PMOS transistors to form p regions. Next, a conformal spacer dielectric layer is deposited on the wafer and anisotropically etched back, leaving sidewall spacers along the edges of the polysilicon gates. After growing a thin screen oxide for the following implantation, the source/drain regions of the NMOS and PMOS transistors not protected by the sidewall spacer are successively implanted to form n<sup>+</sup> and p<sup>+</sup> regions, respectively. The final step of the source/drain engineering is a furnace anneal, typically at ~ 900 °C for 30 min, to activate the implants, anneal implant damage and drive the junctions to their final depth. Alternatively to the furnace anneal, a much shorter rapid thermal anneal at higher temperatures can be performed (e.g. 1 min at 1000–1050 °C). The fabrication of the active devices is now completed. Any subsequent high-temperature step (above 700-800 °C) necessary for the MEMS fabrication must be carefully qualified, as it might affect the doping distributions in the active devices, thus potentially changing the device characteristics.

In the back end of the process, the individual active devices are interconnected on the wafer to form circuits and pads for input/output connections off the chip are created. Although a large number of back-end metallization process flows with up to eight metallization levels exist, the exemplary CMOS process described in [6] uses three metallization levels with a local interconnect level based on titanium nitride and two wiring levels based on aluminum. The contacts to the source/drain regions and to the gate polysilicon are based on titanium silicide (TiSi<sub>2</sub>). To this end, a thin titanium layer (50-100 nm) is sputtered on the wafer after removal of the implantation oxide. During an annealing step at about 600°C in N2, the titanium reacts with Si where they are in contact (e.g. source, drain and gate polysilicon) to form TiSi2 and with N2 to form TiN elsewhere. The resulting TiN layer is patterned to create a local interconnect. Subsequently, the wafer surface is typically planarized using a PSG (phosphosilicate glass) or BPSG (borophosphosilicate glass) layer reflown at 800-900 °C. Modern CMOS processes often

use chemical mechanical polishing (CMP) for interconnect and interconnect dielectric planarization. In the process described in [6], each of the following wiring levels uses CVD tungsten vias with a TiN adhesion/barrier layer and an aluminum (with a small percentage of Si and Cu) interconnect layer. Finally, the passivation layer is deposited (typically by PECVD) and patterned to form the pad openings necessary to contact the device from the outside. The composition of the passivation layer and especially its residual stress can be adapted according to the needs of the microstructures (see Section 1.3.1). After passivation, the wafers are annealed at low temperatures (400-450°C) for about 30 min in forming gas (10%  $H_2$  in  $N_2$ ) to alloy the metal contacts.

The CMOS process presented in [6] and briefly described here requires 16 masks. A schematic device cross-section is shown in Fig. 1.2.

#### 1.1.3

#### CMOS Materials for Micro- and Nanosystems

The particular CMOS technology chosen for the implementation of a micro- or nanoelectromechanical system (MEMS or NEMS) dictates the overall process sequence, the doping profiles and junction depths of doped silicon regions, and the material properties and thicknesses of the different thin-film layers. In general, only minimal adaptations can be made in order not to compromise the performance of the CMOS circuits (see Section 1.3). However, the different layers of the CMOS process can be used for the fabrication of the microstructures themselves. Tab. 1.1 summarizes the different doping regions and layers of a typical CMOS process and their use in MEMS and NEMS.

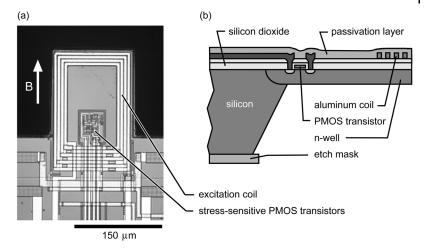

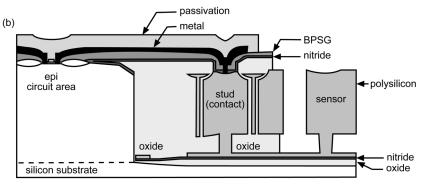

Two examples, namely a CMOS-based mass-sensitive chemical sensor [19-21] and a CMOS-based thermal imager [22, 23], will be discussed in the following. The mass-sensitive chemical sensor (see Fig. 1.6) is based on a 150 µm long and 140 µm wide cantilever beam consisting of the n-well of the CMOS process covered by the CMOS dielectrics [21]. Thus, the n-well and the CMOS dielectrics are used as structural materials. The cantilever is released after completion of the CMOS process by three post-CMOS micromachining steps: first, a silicon membrane is formed by anisotropic wet etching from the back of the wafer in combination with an electrochemical etch-stop technique at the p-n junction between psubstrate and n-well; thereafter, the cantilever is released by two reactive ion etching (RIE) steps. The two aluminum metallization layers are used to form a planar coil on top of the cantilever, enabling the generation of transverse vibrations in the presence of an external DC magnetic field parallel to the cantilever length. The transverse vibration are detected with stress-sensitive diode-connected PMOS transistors, arranged in a Wheatstone bridge configuration at the cantilever's clamped edge. Alternatively, piezoresistors can be formed using either the p<sup>+</sup>source/drain implantation of a PMOS transistor or the n<sup>+</sup>-doped gate polysilicon. The cantilever beam is coated with a chemically sensitive polymer layer. Upon absorption of analyte in the polymer layer, the cantilever's mass increases and, hence, its resonance frequency decreases. The change of resonance frequency is

**Tab. 1.1** Common CMOS materials and their use in micro- and nanoelectromechanical systems (MEMS and NEMS)

| CMOS layer/structure                                    | Use in MEMS and NEMS                                                                           |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------|

| n-well/p-well                                           | Structural material<br>Thermal conductor/mass                                                  |

| Source/drain implantation                               | Resistor<br>Piezoresistor<br>Thermopile<br>Electrode                                           |

| Field oxide                                             | Structural material<br>Thermal insulator<br>Sacrificial material                               |

| Gate polysilicon<br>(and optional 2nd polysilicon)      | Resistor Piezoresistor Thermopile Electrode Structural material Sacrificial material           |

| Contact and intermetal oxides                           | Structural material<br>Thermal insulator<br>Sacrificial material                               |

| Metallization (and optional multi-level metallizations) | Conductor Mirror Thermal conductor Electrode Structural material Sacrificial material          |

| Passivation                                             | Structural material<br>Thermal insulator<br>Stress compensation<br>Infrared radiation absorber |

sensed by incorporating the resonant cantilever into an amplifying feedback loop [20, 21].

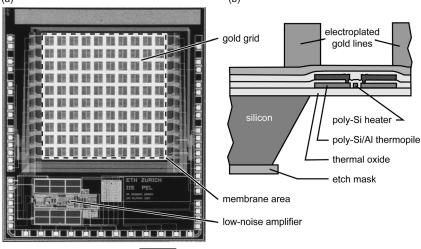

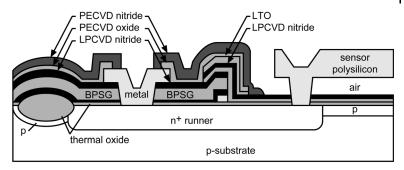

The thermal imager shown in Fig. 1.7 is based on a  $\sim 3\times3$  mm<sup>2</sup> membrane consisting of the dielectric layers of the CMOS process [22, 23]. The membrane is released by wet anisotropic silicon etching from the back of the wafer after completion of the regular CMOS process sequence. The thick field oxide is used as an intrinsic etch-stop layer. The CMOS dielectrics, i.e. the field oxide, the contact oxide, the intermetal oxide and the passivation, are used as structural materials. A grid of electroplated gold lines provides additional structural support to the membrane and divides it into 100 pixels. The gold lines are electroplated after the CMOS process in a standard process step normally preparing the wafers for TAB (tape automated bonding). Sandwiched in between the CMOS dielectrics on each pixel is a polysilicon/aluminum thermopile and a polysilicon heating resistor. The

Fig. 1.6 (a) Photograph and (b) schematic cross-section of a cantilever-based mass-sensitive gas sensor. The cantilever structure features an integrated planar coil for electromagnetic excitation of transverse vibrations in the

presence of a DC magnetic field and PMOS transistors in a Wheatstone bridge arrangement for deflection detection [21]. Photograph courtesy of C. Vancura, ETH Zurich, Switzerland

incoming infrared (IR) radiation is absorbed in the CMOS thin-film sandwich

1 mm

Fig. 1.7 (a) Photograph and (b) schematic cross-section of a CMOS-based infrared radiation sensor array. The sensor array is located on a micromachined membrane consisting of the dielectric layers of the CMOS process. An electroplated gold grid divides the membrane in a  $10 \times 10$  array of pixels, each incorporating

a thermopile with 16 polysilicon/aluminum thermocouples for temperature sensing. Onchip circuitry includes a multiplexer and a low-noise chopper amplifier [22, 23]. Photograph courtesy of Prof. H. Baltes, ETH Zurich, Switzerland

(including the passivation), resulting in a measurable temperature elevation of the individual pixels. All structures necessary for IR radiation sensing are completely formed within the regular CMOS process sequence [22, 23].

# 1.1.4 **CMOS Microsystems**

A number of microsensors can be completely formed within the regular CMOS process sequence, typically not requiring any additional process steps. Well-known examples include temperature sensors [24, 25], magnetic field sensors (especially Hall sensors) [26] and CMOS imagers [27, 28]. An additional subset of CMOSbased microsystems only requires either the modification of a CMOS layer or the deposition and patterning of additional layers, but no micromachining steps. A few selected examples will be given in the following.

Chemical sensors and biosensors relying on an electrochemical sensing principle require an electrode in contact with the sample to be sensed. Examples include amperometric sensors, palladium-gate FET and ISFET (ion-sensitive field effect transistor) structures, and also chemoresistors and chemocapacitors. A number of these electrochemical sensors have been co-integrated with CMOS circuitry (see Chapter 7), typically requiring deposition and patterning of special metal electrodes and/or passivation layers in addition to the regular CMOS process sequence.

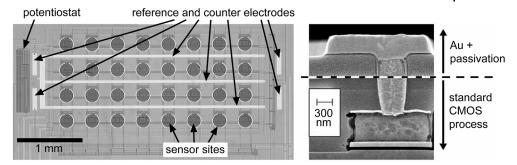

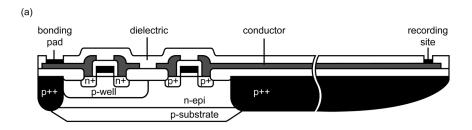

Examples are the CMOS-based biosensor arrays developed recently for DNA analysis [29, 30] and recording of neural activity [31]. The sensor arrays are based on a standard 0.5 μm CMOS process optimized for analog applications [30]. After deposition and patterning of the second aluminum layer, a silicon dioxide layer is deposited, followed by a planarization step using CMP and the deposition of a silicon nitride passivation. The actual sensor electrodes are fabricated on top of the nitride passivation. First, vias are etched to enable contacts to the aluminum metallization and are filled with a Ti/TiN barrier layer and CVD tungsten [30]. In the case of the DNA arrays, the final interdigitated gold electrodes are deposited by evaporation of a Ti/Pt/Au electrode stack, which is patterned using a lift-off technique ([30]; see Fig. 1.8). In the case of the sensor arrays for neural activity recording, the sensor electrodes and the contact pads are defined by depositing and liftoff patterning of a Ti/Pt layer. Subsequently, a dielectric layer sandwich consisting of different TiO2 and ZrO2 layers is deposited and opened at the location of the bond pads. Neural activity is recorded capacitively with the sensor electrodes covered by the protective dielectric layer sandwich. Finally, a gold layer is deposited on the Pt pads and structured using a lift-off process [31].

Researchers at ETH Zurich have recently reported a CMOS-integrated microelectrode array for stimulation and recording of natural neural networks [32]. The microsystem is fabricated using a 0.6 µm CMOS process in combination with a two-mask post-CMOS process sequence to deposit and pattern biocompatible platinum electrodes. The post-CMOS process sequence starts with the deposition and patterning of 50 nm TiW and 270 nm Pt. The metal layer sandwich is structured

Fig. 1.8 (a) Photograph of an  $8\times4$  element DNA sensor array with a single sensor diameter of 200  $\mu$ m and a sensor pitch of 400  $\mu$ m; (b) SEM photograph of sensor cross-section

showing the standard CMOS metallization, the tungsten vias and the gold sensor electrodes. Adapted from [30]

using a lift-off technique. Finally, a 1  $\mu$ m silicon nitride sealing layer is deposited by PECVD and patterned with RIE.

A CMOS-based biochemical multisensor microsystem requiring no micromachining has been developed by IMEC, K. U. Leuven and Siemens [33]. The microsystem combines, on a single CMOS chip, an array of ISFETs, an amperometric oxygen sensor and a conductometric cell. The biochemical analysis system is based on double-metal, 1.2 μm CMOS technology. A special ISFET module has been integrated into the regular CMOS process sequence to form a protective LPCVD nitride layer on top of the ISFET gates. In addition, Ti/Pt electrodes for the amperometric sensor are deposited and patterned and Ag/AgCl reference electrodes are formed by electroplating and electrochloridation [33, 34]. ISFET structures requiring no modifications to the CMOS process sequence have been presented in [35].

Capacitive chemical microsensors based on interdigitated metal electrodes can be fabricated completely within the regular CMOS process sequence. Examples include microsensors for detection of humidity [36, 37] and volatile organic compounds in air [38, 39]. Typically, the interdigitated electrode structure is formed by the metallization layers of the CMOS process. The capacitive sensor structure detects changes in the dielectric constant of a sensing layer deposited on top of it upon absorption of analyte molecules. CMOS-integrated capacitive humidity sensors are produced by Sensirion, Switzerland [40, 177].

Hall plates can be formed completely within a regular (Bi)CMOS process sequence and Hall sensor systems with on-chip circuitry are commercially available, e.g. from Micronas [41], Infineon Technologies [42], Allegro Microsystems [43] and Melexis [44]. Regular Hall plates are arranged parallel to the chip surface and are sensitive to magnetic fields perpendicular to the chip surface. Using spinning-current methods for offset reduction, commercially available CMOS integrated Hall sensors have offsets as low as 0.5 mT [45]. To improve sensor performance, i.e. sensitivity and offset, the Hall sensors have been combined with integrated magnetic flux concentrators by bonding and patterning thin high-permeability,

low-coercivity ferromagnetic layers to the chip surface [46]. In addition to concentrating the magnetic flux at the location of the Hall sensors, the flux concentrators allow the measurement of magnetic fields in the chip plane with standard lateral Hall sensors [46]. Alternatively, magnetic fields parallel to the chip surface can be sensed by vertical Hall sensors, rotated 90° to the chip surface [47, 238]. Recently, CMOS-based vertical Hall sensors have been fabricated by developing a pre-CMOS trench etching technology to define the geometry of the Hall plates ([47]; see Section 1.4.1).

Ferromagnetic films not only are used in combination with Hall sensors, but are also essential for highly sensitive fluxgate sensors. The operation of a fluxgate sensor requires a ferromagnetic core which needs to be saturated periodically by the control circuitry. CMOS-based fluxgate sensors with minimal detectable magnetic fields in the nanotesla range (typical noise levels in the range 5-100 nT/  $\sqrt{\text{Hz}}$ ) have been demonstrated at the Fraunhofer Institute IMS [48, 49], ETH Zurich [50, 51] and EPF Lausanne [52]. In [49], a ferromagnetic Ni<sub>81</sub>Fe<sub>19</sub> core is embedded in the intermetal dielectrics between the two metallization layers of a CMOS process. In this way, the required excitation and pick-up coils consisting of metal-1 and metal-2 lines can be wound around the core. The electron beam-evaporated nickel-iron cores are sandwiched between tantalum layers, serving as adhesion layers and diffusion barriers. The metal sandwich is patterned using liftoff techniques. In [50, 51], two 1 µm thick ferromagnetic NiFeMo cores are electroplated on top of the CMOS chip. Finally, the approach presented in [52] uses a soft-magnetic amorphous alloy (Metglas 2714A, Honeywell), which is mounted on top of the CMOS die and structured using a photolithographic process.

The final two examples both require a direct contact with the surface of a CMOS chip during sensing. Fingerprint sensors are used for access control and authentication and are covered in detail in Chapter 8. In the case of a capacitive sensor, a two-dimensional electrode array measures the capacitance between the chip surface and the finger's surface touching the chip with a resolution of typically 500 dpi. The fingerprint sensor developed by Siemens is based on a doublemetal, 0.8 μm CMOS process and features, on a single chip, a 256×256 pixel sensor array with a pitch of 50 µm, the necessary data acquisition circuitry, A/D conversion and a parallel interface [53]. The sensor is protected against electrostatic air discharge, caused by touching the sensor with a charged finger, using a grounded refractory metal grid (see Chapter 8).

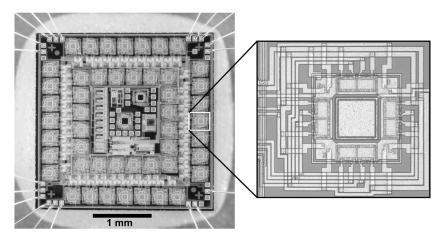

Wire bonding remains the predominant method for providing electrical interconnections between chip and substrate. Increasing bonding speed paired with decreasing pad-pitch requires careful optimization of the wire bonding process and a profound understanding of the physical processes occurring during the actual bonding process. Recently, CMOS-based force sensors have been developed for in situ investigation of the forces acting on the bond pad during thermosonic ballwedge wire bonding [54, 55]. The test chips comprise an array of xyz-force sensors connected to a multiplexer (see Fig. 1.9). Each xyz-sensor features three Wheatstone bridges with piezoresistors to measure the x, y and z-components of the force acting on the bond pad during the wire bonding process. The p<sup>+</sup> and n<sup>+</sup>

Fig. 1.9 Test chip with 48 xyz-force sensors connected to a multiplexed bus; the close-up of one xyz-force sensor shows the test pad

with a size of 65  $\mu m$  and the surrounding piezoresistors for x, y and z-force sensing [54]

source/drain implantations of a double-metal, 0.8 µm CMOS process are used to form the piezoresistors surrounding the bond pad. Hence, the force sensors can be completely formed within the regular CMOS process sequence, potentially allowing the implementation of bonding test structures into regular CMOS designs.

In all of the above cases, no micromachining steps are involved. The focus of the remainder of this chapter (and the main focus of this book) is on CMOS-based micro- and nanosystems requiring either bulk or surface micromachining to release micromechanical structures.

# 1.2 CMOS-compatible Micromachining Process Modules

The basic microfabrication processes described earlier are often combined with special micromachining steps to produce (three-dimensional) microstructures, such as cantilevers, bridges and membranes. In the following, the fundamental micromachining techniques are reviewed. More details on micromachining techniques can be found in dedicated books on microsystem technology [56–59].

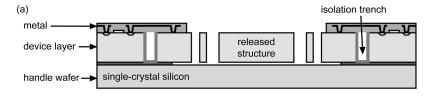

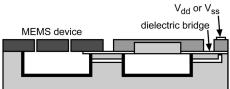

The micromachining techniques are categorized into bulk micromachining [60] and surface micromachining processes [61] (see Fig. 1.10). In the case of bulk micromachining, the microstructure is formed by machining the relatively thick bulk substrate material, whereas in the case of surface micromachining, the microstructure comprises thin-film layers, which are deposited on top of the substrate and selectively removed in a defined sequence to release the MEMS structure.

Fig. 1.10 Schematic of (a) bulk and (b) surface micromachining

# 1.2.1 Bulk Micromachining

Bulk micromachining techniques [60], i.e. etching techniques to machine the (silicon) substrate, can be classified into isotropic and anisotropic, and into wet and dry etching techniques, as can be seen in Tab. 1.2.

The most common *isotropic wet* silicon etchant is HNA, a mixture of hydrofluoric acid (HF), nitric acid (HNO<sub>3</sub>), and acetic acid (CH<sub>3</sub>COOH). In this etching system, nitric acid oxidizes the silicon surface and hydrofluoric acid etches the grown silicon dioxide layer. The acetic acid controls the dissociation of HNO<sub>3</sub>, which provides the oxidation of the silicon. The etch rates and the resulting surface quality strongly depend on the chemical composition [58].

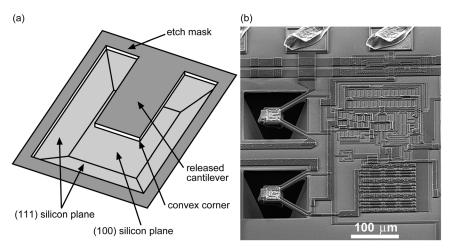

Anisotropic wet etching of silicon is the most common micromachining technique and is used to release, e.g. membrane and beam structures. Anisotropic wet etchants etch single-crystalline silicon with different etch rates along different crystal directions. The resulting etch grooves are bound by crystal planes, along which etching proceeds at slowest speed, i.e. the (111) planes of silicon. In case of the commonly used (100) silicon wafers, the (111) planes are intersecting the wa-

| Tab. 1.2 | Examples of | f etching | techniques | for | machining | the | silicon | substrate |

|----------|-------------|-----------|------------|-----|-----------|-----|---------|-----------|

|----------|-------------|-----------|------------|-----|-----------|-----|---------|-----------|

| Түре        | Wet etching                                                                                                                                                                                         | Dry etching                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Isotropic   | HNA system<br>HF–HNO <sub>3</sub> –CH <sub>3</sub> COOH                                                                                                                                             | Vapor-phase etching<br>XeF <sub>2</sub> |

| Anisotropic | Alkali metal hydroxide solutions<br>KOH, NaOH<br>Ammonium hydroxide solutions<br>(CH <sub>3</sub> ) <sub>4</sub> NOH (TMAH), NH <sub>4</sub> OH<br>EDP solutions<br>Other solutions, e.g. hydrazine | Plasma etching<br>RIE, deep-RIE         |

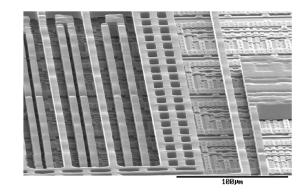

fer surface at an angle of 54.7°, yielding the typical pyramid-shaped etch grooves shown in Fig. 1.11. Masking materials for anisotropic silicon etchants are silicon dioxide and silicon nitride. It is important to note that 'convex' corners of the etch mask (as shown in Fig. 1.11) are underetched in the case of (100) silicon substrates, leading to, e.g., completely underetched cantilever structures. The etch rates in preferentially etched crystal directions such as the \( 100 \) and the \( 110 \) directions, and the ratio of the etching rates in different crystal directions depend strongly on the exact chemical composition of the etching solution and the process temperature [57, 58, 60, 62].

The most common anisotropic silicon etching solution is potassium hydroxide, KOH. As an example, a 6-M KOH solution at 95 °C provides a (100) etch rate of 150  $\mu$ m/h and an anisotropy, i.e. etch rate ratio, between the  $\langle 100 \rangle$  and  $\langle 111 \rangle$  directions of 30-100:1 [63]. Since the etch rate of silicon dioxide in KOH solutions is fairly high (for thermal oxide  $\sim 1 \,\mu\text{m/h}$  in 6 M KOH solution [58]), silicon nitride films are often used as etching mask. KOH solutions are very stable, yield reproducible etching results and are relatively inexpensive. KOH is, therefore, the most common anisotropic wet etching chemical in industrial manufacturing. The disadvantages of KOH include the relatively high SiO2 and Al etch rates, which require protection of IC structures during etching. Etching with KOH is typically performed from the back of the wafer, with the front side protected by a mechanical cover and/or a protective film [63]. Another issue is the detrimental impact of

Fig. 1.11 (a) Schematic of a cantilever beam released by anisotropic silicon etching from the front side of the wafer. The etching mask defines the cantilever shape. The underetching of the cantilever structure starts at convex corners. The resulting etch groove is bound by characteristic (111) side walls and a (100) bottom surface. (b) SEM photograph showing

two bulk-micromachined thermal converters cointegrated with CMOS circuitry. The devices are released from the front side of a CMOS wafer by combining anisotropic silicon etching using TMAH with an electrochemical etch-stop technique. SEM photograph courtesy of Prof. G.T.A. Kovacs, Stanford University, USA

alkali metal ions on the characteristics of MOSFET structures. Investigation of MOSFET characteristics after KOH etching from the back of CMOS wafers, however, did not reveal any etching-related damage [63].

Alternative silicon etchants are ammonium hydroxide compounds, such as tetramethyl ammoniumhydroxide (TMAH), and ethylenediamine–pyrocatechol (EDP) solutions. Certain EDP formulations, such as EDP type S, exhibit relatively low Al and SiO<sub>2</sub> etch rates, which make them suitable for releasing microstructures from the front side of CMOS wafers [232]. However, EDP solutions age rapidly, are potentially carcinogenic and are very difficult to dispose of. TMAH solutions exhibit similar etching characteristics to EDP, but are easier to handle. By controlling the pH by, e.g., dissolving silicon in the etching solution, the etch rate for aluminum metallizations can be reduced [60, 64], making TMAH also a candidate etchant for releasing microstructures from the front side of CMOS wafers. More detailed discussions of wet etching of silicon can be found, e.g., in [57, 58].

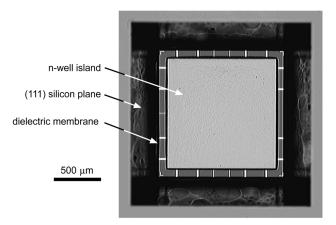

Reliable etch stop techniques are very important for achieving reproducible etching results. As already mentioned, wet anisotropic silicon etchants 'stop' etching, i.e. the etch rate is reduced by at least 1–2 orders of magnitude, as soon as a (111) silicon plane or a silicon dioxide (or silicon nitride) layer is reached. In addition, the etch rate is greatly reduced in highly boron doped regions (doping concentration  $\geq 10^{19}$  cm<sup>-3</sup>). The etching can also be stopped at a p–n junction using a so-called electrochemical etch stop technique (ECE) [56, 65]. This method has been extensively used to release silicon membranes and n-well structures (see Fig. 1.12). ECE relies on the passivation of silicon surfaces when an anodic potential is applied that is sufficiently high with respect to the potential of the etching solution.

Fig. 1.12 Micrograph of an anisotropically etched cavity of a capacitive chemical microsystem (see Chapter 7, Fig. 7.32). At the bottom of the cavity, an n-well island structure carrying a thermally stabilized capa-

citive sensor [67] is visible. The n-well is suspended by a membrane consisting of the CMOS dielectric layers (the embedded metal interconnects connecting the sensor are clearly visible)

Isotropic dry etching of silicon can be done using xenon difluoride, XeF<sub>2</sub>. This vapor-phase etching method exhibits excellent etch selectivity with respect to aluminum, silicon dioxide, silicon nitride and photoresist, all of which can be used as etch masks. However, the resulting etched silicon surfaces are fairly rough. The XeF<sub>2</sub> silicon etch rates depend on the loading (size of the overall silicon surface exposed to the etchant) with typical values of  $\sim 1 \,\mu\text{m/min}$ . XeF<sub>2</sub> etching systems are commercially available from XACTIX [66]. (Alternatively, reactive ion etching (RIE) can be used for isotropic dry etching see also anisotropic dry etching below).

Anisotropic dry etching of silicon is usually performed by reactive ion etching (RIE) in plasma-assisted etching systems. By controlling the process parameters, such as process gases and process pressure, the etching can be rendered either isotropic or anisotropic. The dry-etching anisotropy mainly originates from the direction of ion bombardment, and is, therefore, independent of the crystal orientation of the substrate material. Most bulk etching of silicon is accomplished using fluorine free radicals with SF<sub>6</sub> as a typical process gas. Adding chlorofluorocarbons results in polymer deposition in parallel with etching, which leads to enhanced anisotropy.

Very high aspect ratio microstructures can be achieved with deep (D)RIE, a method which has gained importance during recent years. DRIE systems rely on high-density plasma sources and an alternation of etching and polymer-assisted sidewall protection steps. In a process known as the Bosch process [68], a mixture of trifluoromethane and argon is used for polymer deposition. Owing to the ion

| Tab. 1.3  | Comparison of characteristics of common bulk silicon etchants; the etch rates given          |

|-----------|----------------------------------------------------------------------------------------------|

| are typic | al numbers, the actual etch rates depend on the process parameters (sources for etch-        |

| ing rates | s and selectivities: HNA [9, 58], KOH [58], TMAH [57, 72], XeF <sub>2</sub> [66], DRIE [57]) |

|                                                 | HNA                                | КОН<br>6 М       | TMAH<br>22%                      | XeF <sub>2</sub>    | DRIE                    |

|-------------------------------------------------|------------------------------------|------------------|----------------------------------|---------------------|-------------------------|

| Etch type                                       | Wet                                | Wet              | Wet                              | Dry                 | Dry                     |

| Anisotropic?                                    | No                                 | Yes              | Yes                              | No                  | Yes                     |

| Si (100) etch<br>Rate <sup>a)</sup><br>(µm/min) | typically > 3<br>at 25 °C          | 2.5<br>at 95°C   | 0.6<br>at 80°C                   | typically 1         | 2–3                     |

| SiO <sub>2</sub> etch rate (nm/min)             | 30–70<br>at 25 °C                  | 15<br>at 95°C    | 0.1<br>at 80°C                   | 1:10000°)           | 1:120-200 <sup>c)</sup> |

| SiN <sub>x</sub> etch rate (nm/min)             | No data<br>available <sup>b)</sup> | ≤0.01<br>at 95°C | 1:3600 <sup>c)</sup><br>at 95 °C | 1:100 <sup>c)</sup> | No data<br>available    |

| ECE etch stop?                                  | Yes                                | Yes              | Yes                              | No                  | No                      |

| Cost                                            | Low                                | Low              | Low                              | High                | High                    |

For isotropic etchants, the etch rate is independent of the crystal orientation; for anisotropic dry etching, the etch rate given is in direction of the ion bombardment.

$SiN_x$  etch rate in HNA is smaller than  $SiO_2$  etch rate.

Selectivities between etch rates SiO<sub>2</sub>: Si and SiN<sub>x</sub>: Si are given rather than etch rate itself

bombardment, the polymer deposition on the horizontal surfaces can almost be prevented, while the sidewalls are passivated with a Teflon-like polymer. In the second process step, SF<sub>6</sub>-based etching chemistry provides silicon etching in the non-passivated regions, i.e. the horizontal surfaces. Both process steps are alternated, resulting in typical silicon etch rates of 1-3 μm/min with an anisotropy of the order of 30:1 [60]. Silicon dioxide and photoresist layers can be used as etch masks. The DRIE system achieves exceptional anisotropy, which is independent of the crystal orientation, but is far more expensive than e.g. a simple wet-etching setup, and can process only one wafer at a time. Commercial etchers of this type are available from, e.g., Surface Technology Systems (STS) [69], Unaxis Semiconductor [70] and Alcatel [71].

The characteristics of the most common bulk silicon etchants are summarized in Tab. 1.3. In addition to the described 'basic' micromachining processes, a large number of specific silicon-based micromachining processes have been developed. The ones relevant for the fabrication of CMOS-based microsystems will be discussed in Section 1.4.

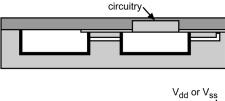

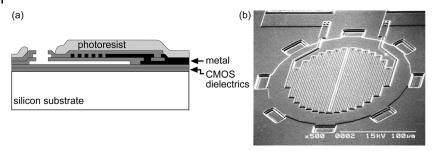

# 1.2.2 Surface Micromachining

The most commonly used surface micromachining process is sacrificial-layer etching [61]. In this process, a microstructure, such as a cantilever beam or a suspended plate, is released by removing a sacrificial thin-film material, which was previously deposited underneath the microstructure. The release of polysilicon microstructures by removing a sacrificial silicon dioxide film is the most popular surface micromachining technique [61]. Sacrificial aluminum etching (SALE) has been developed to release dielectric microstructures with embedded metal layers [73]. Metallic microstructures deposited by low-temperature PVD processes can use polymer films as sacrificial layers, which are removed using, e.g., an oxygen plasma [74, 75].

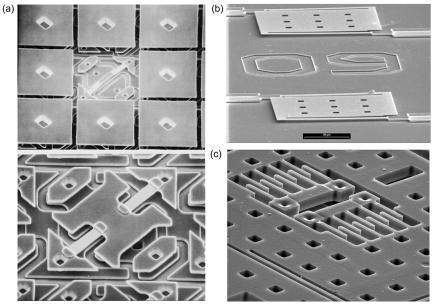

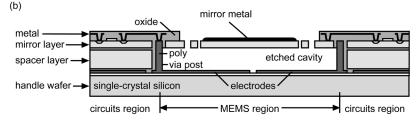

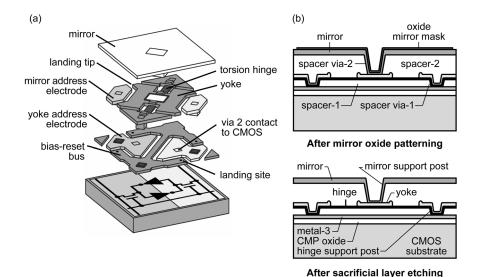

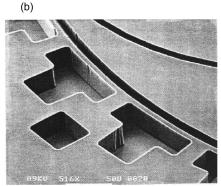

A prominent example of a device based on surface micromachined microstructures is the digital micromirror device (DMD) developed by Texas Instruments ([74], see Section 1.4.3). The DMD consists of an array of micromirrors (see Fig. 1.13a), fabricated on top of a CMOS substrate by deposition and patterning of four metal and two polymer layers. The micromirror array with a pitch of 17 µm is released by removing the polymer sacrificial layers. Fig. 1.13b shows a surfacemicromachined bolometer structure made from polycrystalline Si<sub>57</sub>Ge<sub>43</sub> at IMEC (Leuven, Belgium) and Fig. 1.13c gives details of a 4 µm thick, released polysilicon microstructure fabricated at Analog Devices (Norwood, MA, USA).

Fig. 1.13 (a) Top: SEM photograph of  $3\times3$  array of pixels of Digital Micromirror Device (DMD<sup>TM</sup>) by Texas Instruments; the mirror of the center pixel has been removed to show the underlying metal structures. Bottom: SEM photograph shows details of the micromirror yoke and hinges (images from Texas Instru-

ments DLP image library: http://www.dlp.com). (b) SEM image of surface-micromachined poly-Si57Ge43 bolometer structures. Courtesy of IMEC, Leuven, Belgium. (c) Detail of surface-micromachined 4 µm thick polysilicon microstructure. Courtesy of Steve Lewis, Analog Devices, Norwood, MA, USA

# 1.3 CMOS-compatible Design of MEMS and NEMS

Can I modify the CMOS process sequence to co-integrate microelectromechanical systems with CMOS circuitry? Can I modify the CMOS process design rules to implement my microstructure? Maybe the questions should be less 'Can I?' but rather 'Where and how much can I?'. In the following section, we would like to give the reader an idea of possible process and design modifications. First and foremost, any modification on the CMOS process sequence and the established design rules for a particular process must not compromise the characteristics and yield of the circuitry components. Therefore, every process modification has to be properly qualified. Even if a process modification is not affecting the circuit characteristics, it might be difficult to implement it in a process run done at a commercial CMOS foundry: it can be very challenging to persuade a CMOS foundry to use pre-processed wafers as starting material or to interrupt the regular process sequence and have additional process steps performed (probably even outside the CMOS foundry) before resuming the 'standard' process sequence. We will see in Section 1.4 that

'substantial' process modifications, as required for pre-CMOS and intra-CMOS approaches, most often require in-house CMOS capabilities. In the following, we will concentrate on 'small' process modifications that might be tolerated by a majority of independent CMOS foundries. Since the author's background is especially in the area of post-CMOS microsystem approaches, most of the discussed process modifications will enable different post-CMOS micromachining modules.

### 1.3.1 **Tolerable Process Modifications**

If the microstructures are to be released by wet anisotropic silicon etching (especially from the back of the wafer), the wafer starting material for the CMOS process must be considered carefully. Modern CMOS processes often use epitaxial wafers with a weakly p-doped epitaxial layer on top of heavily p-doped substrate as starting material in order to improve latch-up stability. If the substrate p-type doping is above 10<sup>19</sup> cm<sup>-3</sup>, the silicon etch rates in common anisotropic etchants, such as KOH and TMAH, are drastically reduced. In addition, the starting material has typically a rather broad specification range for the substrate doping, which, in case of highly p-doped substrates, can result in substantial etch rate variations from wafer to wafer. To ensure compatibility with anisotropic silicon etching, either epi-wafers with reduced substrate doping ( $\leq 5 \times 10^{18}$  cm<sup>-3</sup>) or low pdoped non-epi wafers can be used as a starting material [18].

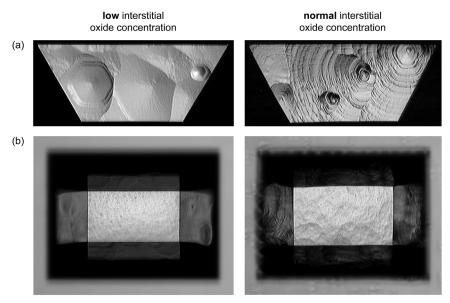

A second challenge for the bulk-micromachining using anisotropic wet etchants is the relatively high interstitial oxygen concentration in the wafer starting material, as required for internal gettering in the CMOS process. With an interstitial oxygen concentration larger than its solid solubility, the oxygen precipitates during annealing steps in the form of oxide particles. Defects caused by oxygen precipitation are commonly used for internal gettering of transition metal impurities during CMOS processing. The oxygen precipitates and the associated crystal defects in CMOS-processed wafers deteriorate the quality of etched cavities, resulting in uneven (111) sidewalls (with crater-like depressions) and large, locally varying underetching of the silicon nitride etch mask, yielding membranes with poor geometric definition [18, 76]. It should be noted that membranes with well-defined lateral dimensions can always be achieved by appropriate design, e.g. using either a p++-doped 'etch-stop' ring surrounding the membrane [77] or an electroplated metal ring [22, 63], defining the mechanical edge of the membrane. A reduction of the interstitial oxygen concentration in the starting material from  $\sim 8 \times 10^{17}$  to  $(6.0-6.9) \times 10^{17}$  cm<sup>-3</sup> resulted in a strongly improved quality of the released microstructures (see Fig. 1.14; [18, 76]). However, the wafer material with reduced defect density also has reduced internal gettering capability and external gettering using, e.g., hard mechanical damage on the wafer back, must be employed. The introduced crystal defects on the wafer back have to be removed at the end of the CMOS process, prior to the deposition of the etch mask.

Any additional (high-temperature) process step performed during or after the regular CMOS process sequence must be considered carefully in terms of the

Fig. 1.14 Quality of etch cavities released by wet anisotropic etching using a 27 wt% (6 M) KOH solution at 90°C; photographs of (a) (111) sidewalls and (b) (100) etch fronts are shown for test wafers with a normal inter-

stitial oxygen concentration of  $\sim 8 \times 10^{17} \text{ cm}^{-3}$ and a low interstitial oxygen concentration of  $(6.0-6.9) \times 10^{17} \text{ cm}^{-3}$ ; prior to KOH etching, the wafers were exposed to a thermal simulation of a CMOS process. Adapted from [18]

overall thermal budget of the process. The overall thermal budget critically influences the various doping profiles and thus the resulting device characteristics. Prolonged additional high-temperature process steps with peak temperatures ≥800 °C are likely only possible prior to the channel and source/drain implantations. Medium-temperature processes, such as LPCVD deposition of polysilicon at about 600°C, have been performed after the source/drain implantations [78], but prior to the back-end aluminum metallization. High-temperature annealing steps required, e.g., for stress relief in the deposited polysilicon layers have to be carefully evaluated, as their thermal budget might influence shallow junction profiles. Of course, the initial doping profiles can be adapted so that additional thermal process steps are taken into account, but this generally requires substantial re-qualification of the CMOS process. The standard aluminum metallization employed in most CMOS processes with minimal feature sizes above 0.25 µm is known to withstand maximum process temperatures of about 450°C (recent work indicates compatibility with temperatures up to 525 °C [79]), strongly limiting the range of process steps that can be performed after completion of the CMOS process sequence (see Section 1.4.3).

Deposition and patterning of the passivation layer are typically the last process steps of the regular CMOS process sequence. Hence, the passivation composition can often be adjusted to the customer's needs. If the passivation is part of the re-

leased microstructure, its residual stress can be used to tune the stress of the overall microstructure. An example is the thermal imager shown in Fig. 1.7. The membrane with embedded infrared sensor array has a layered structure comprising the different dielectric layers of the CMOS process with polysilicon and metal structures sandwiched in between them. The overall stress of the layer sandwich without the CMOS passivation is compressive in this example, which could result in membrane buckling. To reduce the overall compressive stress in the membrane, a passivation layer with tensile stress is deposited. The stress of a PECVD silicon oxynitride passivation could be controlled in the range from -300 to +300 MPa by choosing an appropriate low frequency (400 kHz) to high frequency (13.56 MHz) power ratio and chamber pressure in the used PECVD system [63]. It should be noted that the stress in the passivation can influence the characteristics of the previous layers, e.g. the electromigration behavior of the underlying metal lines.

# 1.3.2 **Design Rule Modifications**

Typically, CMOS foundries provide rule-files for their CMOS processes for a number of supported design environments in order to perform design rule checks (DRCs) and extraction of the layout for layout-versus-schematic (LVS) check. The enforced design rules ensure a high yield of the fabricated circuit components within the given process specifications, but might be problematic for the MEMS part. Two examples are given in the following: in order to release microstructures, such as the thermal converters shown in Fig. 1.11, from the front of the wafer, the silicon substrate must be exposed to the etchant in certain areas on the wafer. This can be achieved in a CMOS process by superimposing an active area (i.e. no field oxide), a contact (i.e. no contact oxide), a via (i.e. no intermetal oxide) and a pad opening (i.e. no passivation), thus locally removing all dielectric layers of the CMOS process and exposing the silicon substrate to the environment [80]. The standard design rules of the used CMOS process will, e.g., not allow a via without metal below and on top of it, because a via in a CMOS circuit only makes sense as an interconnect between two metallization levels. Thus, the automated designrule checker (DRC) will give error messages. In another area one might want to use a non-connected aluminum area as a mirror surface. The DRC will again give an error message because of a non-connected conducting area. Both design examples make no sense in a circuitry environment, but are useful for the MEMS part and, very important, do not compromise the integrity of most CMOS processes (for completeness, it should be mentioned, that sub-0.5 µm CMOS technologies with plated vias might not allow a contact layer without metal overlap in order not to compromise via plug plating and CMP). So, how can one allow such design rule violations and still use the extremely helpful DRC? The ideal case is to write a complete set of design rules for the MEMS areas, having the circuitry checked by the foundry-supplied 'standard' design rule set and the MEMS by an extended design rule set. This approach might be initially more time consuming, but will, in the long run, prevent design errors in the complex MEMS designs.

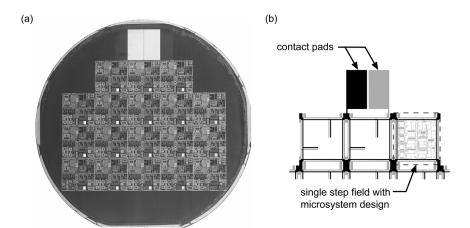

Modern sub-um CMOS processes use lithography based on wafer steppers, providing an array of step fields on the wafer with no mutual connection. Post-CMOS micromachining based on anisotropic wet etching in combination with an electrochemical etch-stop technique (see Section 1.4.3) requires the application of etching potentials to (structural) n-well and substrate contacts across the wafer [17, 18]. To supply these etching potentials, a contact network implemented in the metal-1 and metal-2 level of the CMOS process routes the etching potentials from large contact pads to the individual etch contacts. To achieve this, each metal mask step field is surrounded by a predefined frame (see Fig. 1.26b), routing one etching potential on metal-1 level and the second etching potential on metal-2 level to reduce the risk of short-cuts between the etch networks [18]. The frames are connected to each other at the corners of the step field by metal structures placed in the scribe channel, i.e. the individual metal-level step fields actually overlap during the stepper-based lithography. The construction of these metal bridges must not affect the regular test structures in the scribe channel. Within the reticle, the individual etch contacts are connected to the metal frame. In order to have large contact pads for applying the etch potentials with spring-loaded contacts, a dedicated 'contact' step field (see Fig. 1.26a, top of the wafer) is printed which has the same size as the other step fields. This is done on the second metal mask level using a special 'contact' reticle. In addition, a 'blank' reticle is used to remove the metal around the edges of the wafer in order to avoid short circuits in the etch network at the wafer edge. The described method requires three additional masks ('blank' reticle, 'contact' reticle and 'contact opening' reticle), which can, however, be reused if the reticle size from design to design is not changing. Besides exposing the wafer on the metal mask level with different reticles, no modification in the process flow is required.

# 1.3.3 Simulation of Circuitry and MEMS

Traditionally, MEMS and IC designers have used very different design tools. While IC designers rely on schematic-driven circuit simulators offered by the major electronic design automation (EDA) companies, such as Cadence [81], Mentor Graphics [82] and Synopsys [83], the MEMS designer typically relies on finite-element modeling (FEM) software, such as ANSYS [84], FEMLAB [85], Coventor-Ware [86], or IntelliSuite [87], for multi-domain analysis of their microstructures. In order to simulate and design integrated circuits based on a particular CMOS process, the CMOS foundries supply process-specific design kits, including design rules, process specifications, transistor-level models and analog and digital cell libraries, to support the major EDA tools. In order to simulate CMOS-based microsystems including micromechanical transducers and analog and digital circuitry, behavioral models for the transducer elements are required. To be compatible with the standard mixed-signal simulators delivered with common EDA packages (e.g. SPECTRE [81], ADVance MS [82], SABER [83]), these behavioral models must be expressed in an analog hardware description language (HDL), such as

Verilog-A or VHDL-A. The generation of such models for the transducers involving multiple signal domains from either the layout or the results of the FEM simulation is not straightforward. Simple lumped-element circuit models of the transducers might be developed manually on a case-by-case basis. For certain categories of microstructures (e.g. comb-drive resonators), the generation of macromodels is supported by academic [88, 89] and commercial tools [86, 90]. INTE-GRATOR, developed by Coventor [86], is able to generate reduced-order macromodels of dynamic mechanical systems, consisting of spring, mass and damping elements, from detailed 3-D finite element (FEM) or boundary element (BEM) simulations for export in standard circuit simulators. NODAS, developed at Carnegie Mellon [88, 91, 92] is a library of parameterized components, including beams, plate masses, anchors, electrostatic comb drives and gaps, to simulate surface-micromachined MEMS structures using the SABER and SPECTRE simulators. Complex microstructures are build by interconnecting individual library elements. NO-DAS also has the ability to generate automatically the layout from the developed schematic.

Once the top-level layout of the integrated microsystem is completed, a design rule check (DRC) and a layout-versus-schematic (LVS) check are performed. In order to account for different design rules in the circuitry and the MEMS part, the standard design rule files supplied by the CMOS foundry might need to be extended (see Section 1.3.2). In addition, the standard extraction rules can be adapted in order to recognize and extract at least the electrical features of the transducer elements [93]. This allows the verification of the top-level design by comparison with the simulated top-level schematic and avoids, e.g., wiring errors. Some of the available tools also permit extraction of non-electric features [94].

More details on MEMS modeling in general and the extension of circuit simulation to include micromachined devices can be found in several books and overview articles [94-98].

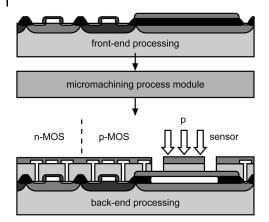

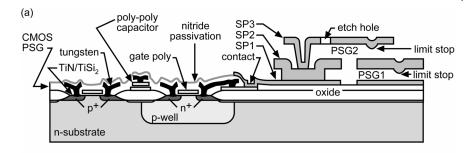

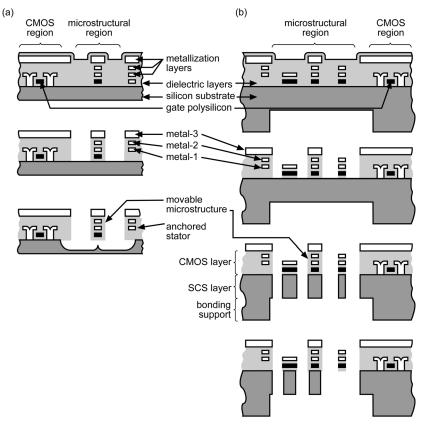

# 1.4 CMOS and Micromachining

The integration of micromachining processes with CMOS technology can be accomplished in different ways. The additional process steps (or process modules) can either precede the standard CMOS process sequence (pre-CMOS) or they can be performed in between the regular CMOS steps (intra-CMOS) or after the completion of the CMOS process (post-CMOS) [99, 100]. In the case of post-CMOS micromachining, the microstructures are built from either the CMOS layers themselves or from additional layers deposited on top of the CMOS wafer. Tab. 1.4 summarizes various CMOS-based microsystem approaches found in the literature. Some of these approaches require several additional process modules, e.g. a pre-CMOS and a post-CMOS module; in these cases, we have categorized them by their first non-standard process sequence. The cited publications are exemplaric and the list provided is by no means considered to be all-inclusive.

Tab. 1.4 CMOS-based microsystems using pre-, intra- or post-CMOS process modules to implement the microstructures

|                             | Surface<br>micromachining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bulk<br>micromachining                                                                                                                                                                                                                 |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pre-CMOS<br>process modules | Sandia National Laboratories (M³EMS) [101]  - Inertial sensors [102] UC Berkeley, Analog Devices, Raytheon and Sandia National Laboratories  - Accelerometer [103] University Michigan  - Accelerometer [104] Analog Devices, Palo Alto Research Center and UC Berkeley (ModMEMS) [105]  - Inertial sensors [106] Analog Devices and UC Berkeley (SOI-MEMS)  - Accelerometer [107, 108] Analog Devices and Clare (Optical iMEMS)  - Optical switches [109] VTT Information Technologies and Micro Analog Systems [110]                                | MIT  - Pressure sensor [111, 112] Univ. Michigan  - Pressure sensor [113] Tohoku Univ.  - Accelerometer [114]  - Pressure sensor [115] Fraunhofer Institute  - Infrared radiation sensor [116] ETH Zurich  - Vertical Hall sensor [47] |  |

| Intra-CMOS process modules  | Analog Devices (iMEMS) [78, 117]  - Accelerometer [107, 118]  - Gyroscope [107, 119]  Infineon Technologies (Siemens)  - Pressure sensor [5, 120, 121]  - Accelerometer [122]  - Ultrasound transducers [123]  Motorola (now Freescale)  - Pressure sensor [124, 125]  Fraunhofer Institute IMS  - Pressure sensor [126–128]  RWTH Aachen and  Fraunhofer Institute IMS  - Pressure sensor [129, 130]  Univ. Duisburg, EPOS and  Fraunhofer Institute IMS  - Tactile sensor [131]  Bosch  - Accelerometer [132]  Toyota  - Pressure sensor [133, 134] | Univ. Michigan  - Pressure sensor [77, 136]  - Mass flow [77]  - Bioprobes [137, 138]  - Thermal converter [139]  - Infrared imager [140]  LG Electronics Inst.  of Technology  and Seoul National Univ.  - Accelerometer [141]        |  |

**Tab. 1.4** (cont.)

|                                                 | Surface<br>micromachining                                                                                                                                                                                                                                                               | Bulk<br>micromachining                                                                                                                                                                                                                                                                                                                                                                                                   |