## 1

**3D IC Integration Since 2008**

*Philip Garrou, Peter Ramm, and Mitsumasa Koyanagi*

In Volume 1, we covered some of the history of the development of the 3D integrated circuit (3D IC) concept and we direct you to that chapter for such content [1].

Since the first two volumes of the *Handbook of 3D Integration* appeared in 2008, significant progress has been made to bring 3D IC technology to commercialization. This chapter will attempt to summarize some of the key developments during that period.

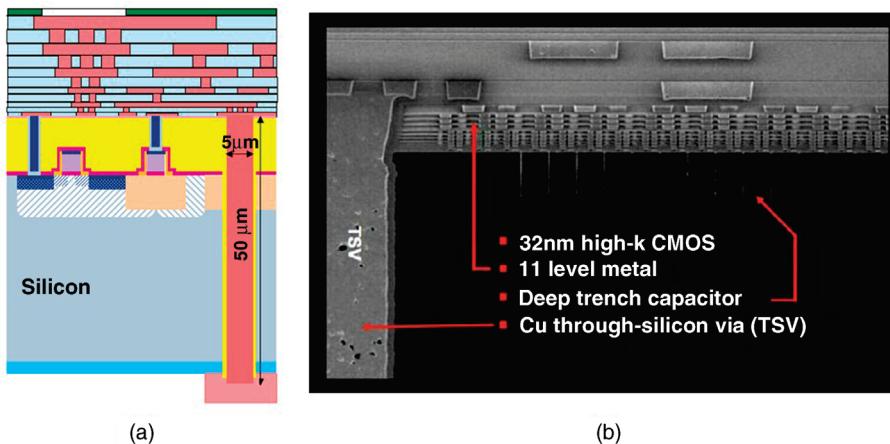

We previously described 3D IC integration as “an emerging, system level integration architecture wherein multiple strata (layers) of planar devices are stacked and interconnected using through-silicon (or other semiconductor material) vias (TSV) in the Z direction” as depicted schematically in Figure 1.1a and in cross section in Figure 1.1b [1].

With the continued pressure to miniaturize portable products and the near universal agreement that scaling as we have known it is soon coming to an end [2], a perfect storm has been created. The response to this dilemma at both the device and the package level has been to move into the third dimension.

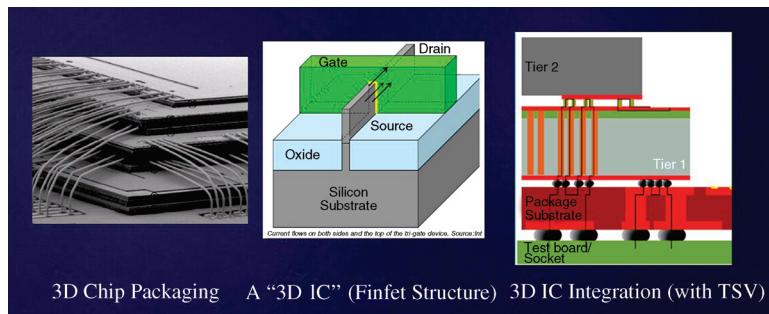

It is commonly accepted that chip stacks wire-bonded down to a common laminate base and stacked packages such as package-on-package (PoP) are categorized as “3D packaging.” Transistor design has also gone vertical [3] as Intel [4] and others move to “finfet” stacked transistor structures at the 22 nm generation. These are compared pictorially in Figure 1.2.

In Figure 1.3, we compare system-on-chip (SoC), 3D packaging, and 3D IC with through-silicon via (TSV) in various performance categories [5].

## 1.1

**3D IC Nomenclature**

Since 2008 there have been attempts to further refine the nomenclature for 3D IC integration, although it has not yet been universally adopted in publications. In 2009 the International Technology Roadmap for Semiconductors (ITRS)

**Figure 1.1** 3D IC with TSV: (a) schematic (courtesy of IMEC) and (b) cross section (courtesy of IBM). Note that the IBM cross section is connected at a higher (fatter) on chip interconnect level.

proposed the following nomenclature in an attempt to define the possible different levels of connections possible as circuits are deconstructed onto separate strata (see Table 1.1) [6].

## 1.2

### Process Standardization

3D IC requires three new pieces of technology: (1) insulated conductive vias through a thinned silicon substrate (i.e., TSV); (2) thinning and handling technology for wafers as thin as  $50\text{ }\mu\text{m}$  or less; (3) technology to assemble and package such thinned chips.

**Figure 1.2** 3D packaging, 3D finfet transistors, and 3D IC integration.

|                   | On-chip SoC | PoP | WB stack | TSV stack |

|-------------------|-------------|-----|----------|-----------|

|                   |             |     |          |           |

| Memory capacity   | -           | ++  | ++       | ++        |

| Memory bandwidth  | ++          | 0   | +        | +++       |

| Power consumption | ++          | 0   | +        | +++       |

| Form factor       | 0           | +   | ++       | +++       |

| Cost              | ---         | -   | ++       | ??        |

Figure 1.3 Comparison of SoC, 3D packaging, and 3D IC [5].

Table 1.1 2009 ITRS roadmap [6].

| Level    | Suggested name                                                  | Supply chain                              | Key characteristics                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-----------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package  | 3D packaging (3D-P)                                             | OSAT assembly printed circuit board (PCB) | <ul style="list-style-type: none"> <li>Traditional packaging of interconnect technologies, for example, wire-bonded die stacks, package-on-package stacks</li> <li>Also includes die in PCB integration</li> <li>No through-Si vias</li> </ul>                                                                                                                                                      |

| Bond-pad | 3D wafer-level package (3D-WLP)                                 | Wafer-level packaging                     | <ul style="list-style-type: none"> <li>WLP infrastructure, such as RDL and bumping</li> <li>3D interconnects are processed after the IC fabrication, “post IC passivation” (via-last process). Connections on bond-pad level</li> <li>TSV density requirements follow bond-pad density roadmaps</li> </ul>                                                                                          |

| Global   | 3D stacked integrated circuit/3D system-on-chip (3D-SIC/3D-SoC) | Wafer fab                                 | <ul style="list-style-type: none"> <li>Stacking of large circuit blocks (tiles, IP blocks, memory banks), similar to an SoC approach but having circuits physically on different layers</li> <li>Unbuffered I/O drivers (low C, little or no ISD protection on TSVs)</li> <li>TSV density requirement significantly higher than 3D-WLP: Pitch requirement down to 4–16 <math>\mu</math>m</li> </ul> |

(continued)

**Table 1.1** (Continued)

| Level        | Suggested name | Supply chain | Key characteristics                                                                                                                                                                                                                                                                 |

|--------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intermediate | 3D-SIC         | Wafer fab    | <ul style="list-style-type: none"> <li>Stacking of smaller circuit blocks, parts of IP blocks stacked in vertical dimensions</li> <li>Mainly wafer-to-wafer stacking</li> <li>TSV density requirements very high: Pitch requirement down to 1–4 <math>\mu\text{m}</math></li> </ul> |

| Local        | 3D IC          | Wafer fab    | <ul style="list-style-type: none"> <li>Sticking of transistor layers</li> <li>Common back-end-of-line (BEOL) interconnect stack on multiple layers of front-end-of-line (FEOL)</li> <li>Requires 3D connections at the density level of local interconnects</li> </ul>              |

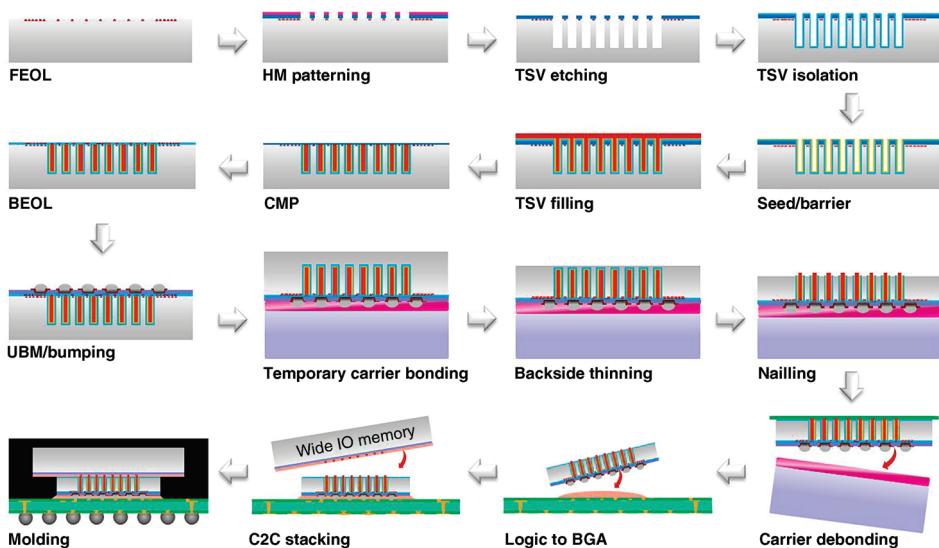

In the mid-2000s, practitioners were bewildered by the multitude of proposed technical routes to 3D IC. It has become clear, since then, that for most applications, the preferred process flow is what has been called a “via-middle” approach, where the TSVs are inserted after front-end transistor formation and early on during the on-chip interconnect process flow. This requires that TSVs are manufactured in back end of fab, not during or after the assembly process. This requires that TSV fabrication will be done by vertically integrated IDMs or foundries. TSV technology appears to be stabilized as depicted in Figure 1.4 and Table 1.2.

### 1.3

#### The Introduction of Interposers (2.5D)

Many believe the introduction of interposers (also known as 2.5D) was due to the failure of 3D IC, but this is not the case. Interposers were and are needed due to the lack of chip interface standardization and the need for a better thermal solution than is currently available for some 3D stacking situations.

The term “2.5D” is usually credited to Ho Ming Tong from Advanced Semiconductor Engineering (ASE), who in 2009 (or even earlier) declared that we might need an intermediate step toward 3D since the infrastructure and standards were not ready yet. The silicon interposer, Tong felt, would get us a major part of the way there, and could be ready sooner than 3D technology, thus the term “2.5D,” which immediately caught on with other practitioners [7].

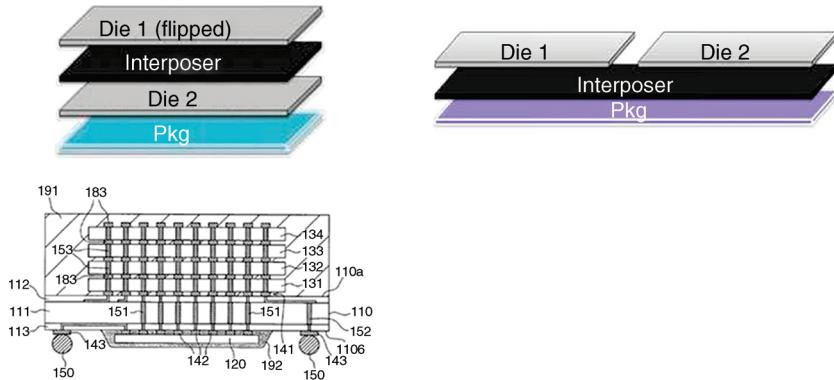

2.5D interposers resemble silicon multichip module technology of the 1990s, with the addition of TSV [8]. In today’s applications, they provide high-density redistribution layers (RDLs), so the chips can be connected either through the interposer or next to each other on the top surface of the interposer as shown in

Figure 1.4 Standard 3D IC process flow. Courtesy of Yole Developpement.

Figure 1.5. The latter is the superior thermal solution since all chips can be attached to a heat sink for cooling.

Interposers will add cost and probably will not be a broadly accepted solution for low-cost mobile products, which would prefer straight 3D stacking [9].

Table 1.2 Standard 3D IC process flow options.

| Process             | Preferred option                       |                                   | Alternative options available |                       |                                               |  |

|---------------------|----------------------------------------|-----------------------------------|-------------------------------|-----------------------|-----------------------------------------------|--|

| TSV formation       | Bosch deep reactive ion etching (DRIE) | Laser                             |                               |                       |                                               |  |

| TSV Insulation      | SiO <sub>2</sub>                       | Polymer                           |                               |                       |                                               |  |

| Conductor           | Cu                                     | W                                 | pSi                           |                       |                                               |  |

| Process flow        | Via-middle                             | Via-last (backside) <sup>a)</sup> | Via-first (for pSi)           | Via-last (front side) |                                               |  |

| Stacking            |                                        |                                   |                               |                       |                                               |  |

| Bonding             | IMC                                    | Cu–Cu                             | Oxide bonding                 | Polymer bonding       | Hybrid bonding (oxide–metal or polymer–metal) |  |

| Thin wafer handling | On carrier                             | On stack                          |                               |                       |                                               |  |

a) Preferred flow for CMOS image sensors.

Figure 1.5 Interposer configurations.

## 1.4 The Foundries

### 1.4.1 TSMC

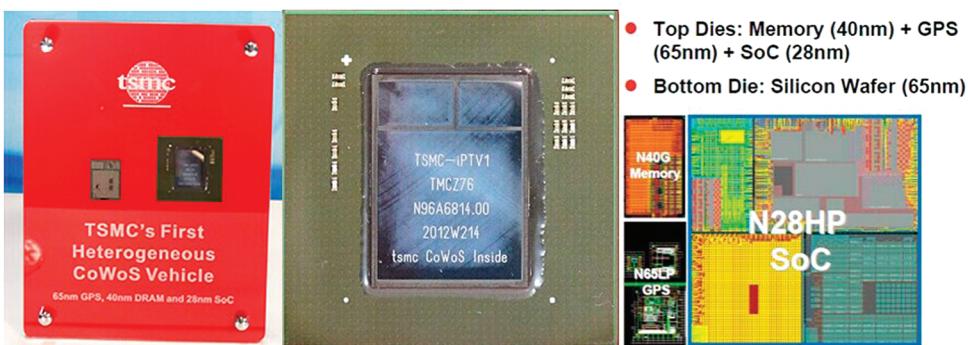

In October 2012, TSMC announced the readiness of their 2.5D CoWoS<sup>TM</sup> (chip-on-wafer-on-substrate) technology within their “Open Innovation Platform<sup>®</sup>” and made public their reference flows supporting CoWoS. Several EDA companies including Cadence, Mentor, Synopsys, and Ansys were announced as partners in the CoWoS reference flow [10]. Their first public CoWoS demonstrator vehicle (Figure 1.6) included logic and DRAM in a single module using the wide I/O interface [11].

Early TSMC customers reportedly included Xilinx, AMD, Nvidia, Qualcomm, Texas Instruments, Marvell, and Altera [12], with Xilinx being the first to production in late 2011.

Figure 1.6 2.5D TSMC demonstrator vehicle [11].

Reportedly due to “. . . the numerous technical challenges that make the conventional collaboration infrastructure more difficult” for 2.5 and 3D IC, TSMC has taken the position of being responsible for the full process (chip design and fabrication through module test).

#### 1.4.2

##### **UMC**

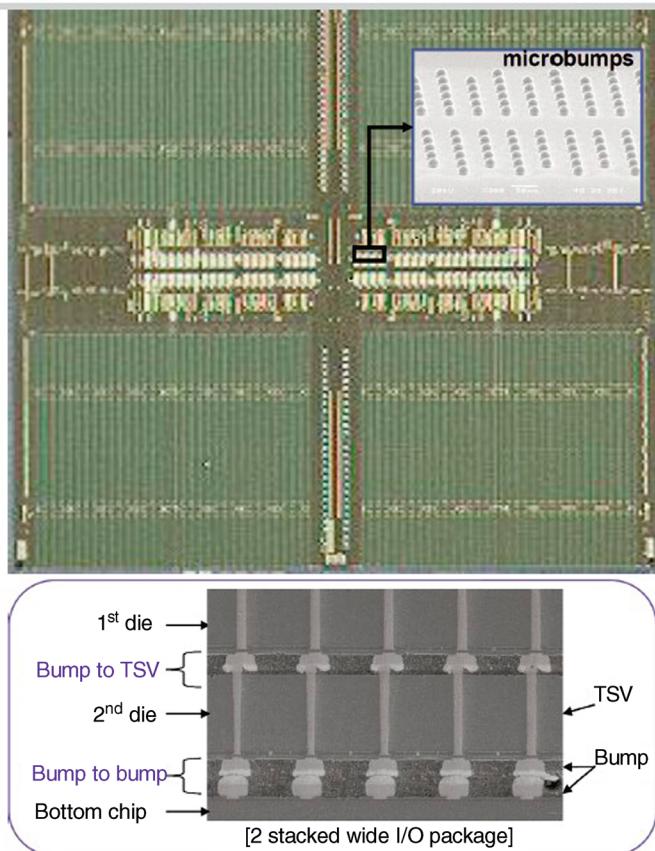

UMC announced in the spring of 2011 that it had acquired production equipment for TSV and other 3D IC technologies. In 2013 UMC and STATS ChipPAC announced a jointly developed TSV-enabled 3D IC chip stack consisting of a Wide I/O memory test chip stacked upon a TSV-embedded 28 nm processor test chip [13].

#### 1.4.3

##### **GlobalFoundries**

GlobalFoundries (GF) announced installation of TSV production tools for 20 nm technology wafers in their Fab 8 New York facility. The first full-flow silicon with TSVs was expected to start running in the third quarter of 2012 [14].

In contrast to TSMC, which announced a one-stop-shop turnkey line that included all of the assembly and test steps traditionally handled by outsourced semiconductor assembly and test (OSAT) facilities, UMC and GlobalFoundries indicated a preference to work under the open ecosystem model where they would handle TSV fabrication (Cu, via-middle) and other front-end steps while chips from various vendors would be back-end processed (i.e., temporary bonding/debonding, thinning, assembly, and test by their OSAT partners).

## 1.5

### **Memory**

DRAM performance is constrained by the capacity of the data channel that sits between the memory and the processor. No matter how much faster the DRAM chip itself gets, the channel typically chokes due to the lack of transfer capacity; that is, they require more bandwidth. Wide I/O memory has been developed as the solution to this bandwidth problem [15].

Also, as more and more memory is required for a given application, power consumption also becomes important to both portable products and server farms, which need special cooling to keep them from overheating. Samsung reports that TSV-based RDIMM shows a 32% decrease in power consumption versus LRDIMM at 1333 Mbps [16].

#### 1.5.1

##### **Samsung**

In late 2010, Samsung, who first revealed 3D TSV stacked memory prototypes in 2006, announced 40 nm, 8 GB RDIMM based on 4 Gb, 1.5 V, 40 nm DDR3

**Figure 1.7**  $1.2\text{ V }12.8\text{ GB s}^{-1}$  2 Gb mobile wide I/O DRAM with  $4 \times 128$  I/Os using TSV-based stacking [18].

memory chips operating at 1333 MHz and 3D TSV chip-stacking technology [17]. In 2011, they announced the development of wide I/O 1 Gb DRAM (Figure 1.7) [18]. Samsung has not announced any commercial memory products as of late 2013. Samsung is a member of the Micron hybrid memory cube consortium.

### 1.5.2

#### **Micron**

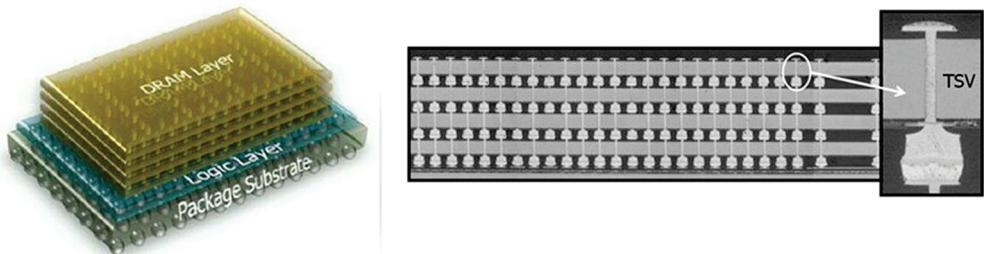

Micron developed a “hybrid memory cube” (HMC), which is a stack of multiple thinned memory dies sitting atop a logic chip bonded together using TSV (Figure 1.8). This greatly increases available DRAM bandwidth by leveraging the large number of I/O pins available through TSVs. The controller layer in the HMC allows a higher speed bus from the controller chip to the CPU and the thinned and TSV connected memory layers mean memory can be packed more densely in a given volume. The HMC requires about 10% of the volume of a DDR3 memory

**Figure 1.8** Micron hybrid memory cube (HMC) [19].

module. It is claimed that the technology provides  $15\times$  the performance of a DDR3 module, uses 70% less energy per bit than DDR3, and occupies 90% less space than today's RDIMMs. Micron has announced that they will be manufacturing the memory layers and have contracted IBM to manufacture the logic layer. Commercialization is scheduled for 2013–2014.

HMC electrical performance is compared to other DRAM modules in Table 1.3.

### 1.5.3

#### Hynix

Hynix reported that they expect “2 and 4 chip memory stacks with TSV to be in commercial production in 2014 and graphics solutions on interposers soon thereafter” [21].

## 1.6

### The Assembly and Test Houses

Amkor was involved with commercial 3D IC assembly as part of their TSMC Xilinx program [22]. ASE, SPIL, and Powertech are all boosting 3D IC package and test capacity. SPIL (Siliconware) announced the instillation of dual damascene processing for high density interposers in 2013 [23]. Powertech, which has been in a 3D IC joint development program with Elpida (now Micron) and UMC for several years, announced volume production of 3D IC packaging and test capability in 2013.

**Table 1.3** Comparison of Micron HMC to DDR memories [20].

| Technology              | VDD | BW (Gb s <sup>-1</sup> ) | Power (W) |

|-------------------------|-----|--------------------------|-----------|

| SDRAM PC133 1 Gb module | 3.3 | 1.06                     | 4.96      |

| DDR-333 1 Gb module     | 2.5 | 2.66                     | 5.48      |

| DDR2-667 2 Gb module    | 1.8 | 5.34                     | 5.18      |

| DDR3-1333 2 Gb module   | 1.5 | 10.66                    | 5.52      |

| DDR4-2667 4 Gb module   | 1.2 | 21.34                    | 6.60      |

| HMC Gen 1 512 Mb cube   | 1.2 | 128.0                    | 10.73     |

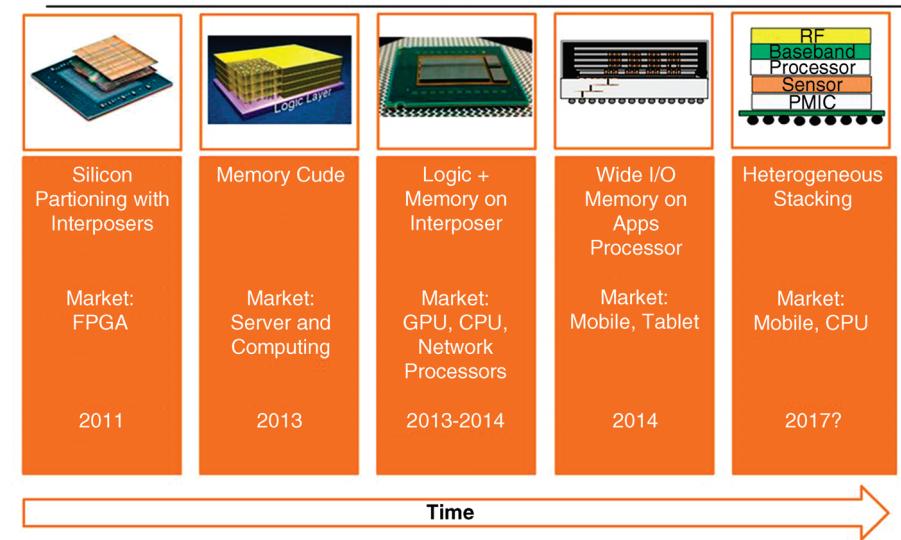

Figure 1.9 3D IC application timing. Courtesy of GlobalFoundries 2012.

## 1.7

### 3D IC Application Roadmaps

The first commercial application has been field-programmable gate arrays (FPGAs) with Xilinx (commercial) [22] and Altera (developing) [24] interposer-based solutions with TSMC.

Looking at the roadmap of GlobalFoundries in Figure 1.9, we see that 2.5D graphics processor modules and 3D application processors with baseband and/or memory should be coming soon.

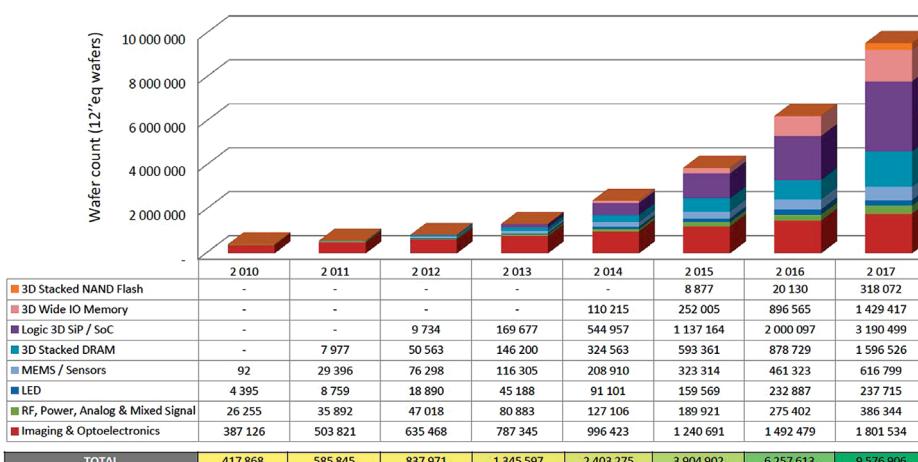

Figure 1.10 TSV chip wafer forecast 2010–2017. Courtesy of Yole Developpement.

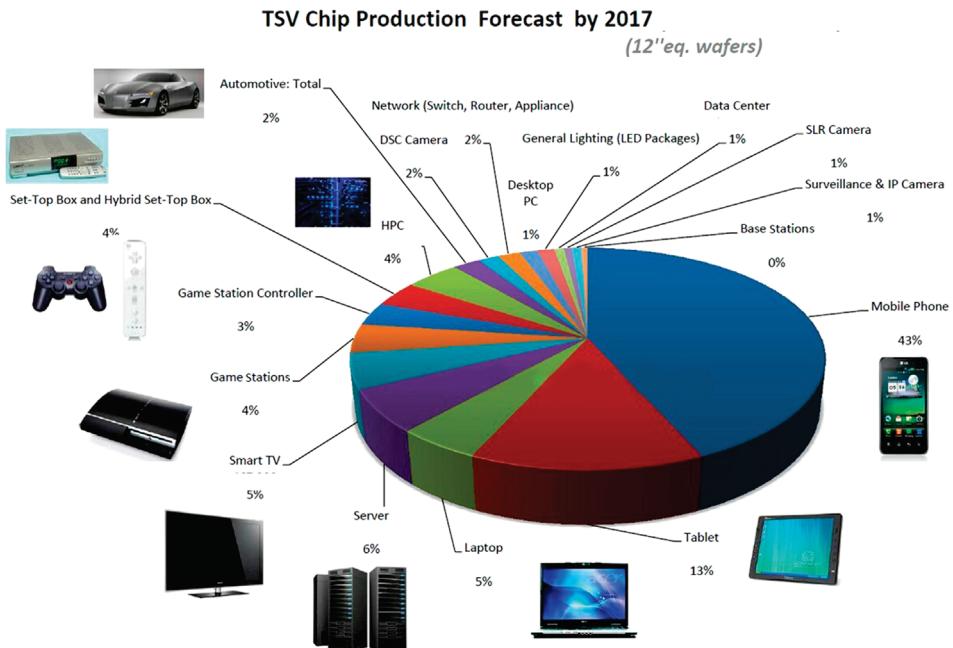

Figure 1.11 Global TSV chip end applications in 2017. Courtesy of Yole Developpement.

The latest projections by Yole Developpement are shown in Figures 1.10 and 1.11. 3D IC volume is expected to increase to nearly 10 MM wafers over the next 4 years with major increases in stacked memory, wide I/O DRAM, and logic plus memory system-in-packages (SiPs).

Examining 2.5/3D device product insertion, we see that most of these devices will eventually be incorporated in the smartphone and tablet markets.

## References

- 1 Garrou, P. (2008) Chapter 1: Introduction to 3D integration, in *Handbook of 3D Integration*, vol. 1 (eds. P. Garrou, C. Bower, and P. Ramm), Wiley-VCH Verlag GmbH, Weinheim.

- 2 Heron, N.Z. (2008) Why is CMOS scaling coming to an end. 3rd International Design & Test Workshop, pp. 98–103.

- 3 Adee, S. (2007) Transistors go vertical. *IEEE Spectrum*, 44, 14.

- 4 James, D. (2012) Intel Ivy Bridge unveiled the first commercial tri-gate, high-k, metalgate CPU. IEEE Custom Integrated Circuit Conference, p. 1.

- 5 Garrou, P. (2011) 3D integration – are we there yet. Suss MicroTech Workshop, Semicon 2011.

- 6 Interconnect (2009) International Technology Roadmap for Semiconductors. Available at [www.itrs.net/links/2009ITRS/2009Chapters\\_2009Tables/2009\\_Interconnect.pdf](http://www.itrs.net/links/2009ITRS/2009Chapters_2009Tables/2009_Interconnect.pdf) (accessed December 31, 2013).

- 7 Garrou, P. (2012) 3.5D interposers to someday replace PWBs – TSMC; GF engaging with 3D customers; Intel predicts Consolidation. Solid State Technology: Insights from the Leading Edge, 102, May 19, 2012.

8 Garrou, P. and Turluk, I. (1998) *Multichip Module Handbook*, McGraw-Hill.

9 Garrou, P. (2013) Interposer supply/ ecosystem examined at IMAPS Device Packaging Conference. Available at [www.electroiq.com/articles/ap/2012/03/interposer-supply-ecosystem-examined-atimaps-device-packaging.html](http://www.electroiq.com/articles/ap/2012/03/interposer-supply-ecosystem-examined-atimaps-device-packaging.html) (accessed December 31, 2013).

10 Garrou, P. (2012) TSMC officially ready for 2.5D, Apple order impact on TSMC. Solid State Technology: Insights from the Leading Edge, 122, November 11, 2012. Available at <http://electroiq.com/insights-from-leading-edge/2012/11/ftle-122-tsmc-officially-ready-for-2-5d-apple-order-impact-on-tsmc/> (accessed December 31, 2013).

11 EDA 360 Insider (2012) 3D Thursday: want to see a closeup of the TSMC 3D IC test vehicle? June 6, 2012. Available at <http://eda360insider.wordpress.com/2012/06/06/3d-thursday-want-to-see-a-closeup-of-the-tsmc-3d-ic-test-vehicle/> (accessed December 31, 2013).

12 Liu, K. (2012) TSC builds up 3DIC assembling capability to vie for lucrative business. *Taiwan Economic News*, August 14, 2012. Available at [http://news.cens.com/cens/html/en/news/news\\_inner\\_40986.html](http://news.cens.com/cens/html/en/news/news_inner_40986.html) (accessed December 31, 2013).

13 Garrou, P. (2013) UMC/SCP memory on logic; SEMI Europe 3D Summit Part 2. Solid State Technology: Insights from the Leading Edge, 135, February 12, 2013. Available at <http://electroiq.com/insights-from-leading-edge/2013/02/ftle-135-umc-scp-memory-on-logic-semi-europe-3d-summit-part-2/> (accessed December 31, 2013).

14 Garrou, P. (2013) GlobalFoundries 2.5/3D at 20 nm; Intel Haswell GT3; UMC/SCP prototype details. Solid State Technology: Insights from the Leading Edge, 142, April 9, 2013. Available at <http://electroiq.com/insights-from-leading-edge/2013/04/ftle-142-globalfoundries-2-5-3d-at-20nm-intel-haswell-gt3-umc-scp-prototype-details/> (accessed December 31, 2013).

15 JEDEC (2012) JEDEC publishes breakthrough standard for wide I/O mobile DRAM. Available at <http://www.jedec.org/news/pressreleases/jedec-publishes-breakthrough-standard-wide-io-mobile-dram> (accessed December 31, 2013).

16 Schauss, G. (2011) Samsung memory solution for HPC. Available at <http://www.ena-hpc.org/2011/talks/schauss-slides.pdf> (accessed December 31, 2013).

17 Kang, U. (2009) 8 Gb DDR3 DRAM using TSV technology. IEEE ISSCC.

18 Kim, J.S. (2011) A 1.2 V 12.8 GB/s 2 Gb mobile wide-I/O DRAM with 4\_128 I/O's using TSV-based stacking. IEEE ISSCC.

19 Jeddelloh, J. and Keeth, B. (2012) New DRAM architecture increases density and performance. 2012 Symposium on VLSI Technology, p. 87.

20 Pawlowski, J.T. (2011) Hybrid memory cube: breakthrough DRAM performance with a fundamentally re-architected DRAM subsystem. Proceedings of the 23rd Hot Chips Symposium.

21 Suh, M. (2013) TSV application in memory devices. RTI 3D Architectures for Semiconductor Integration and Packaging Conference, Burlingame CA, December 2013.

22 Saban, K. (2010) Xilinx stacked silicon interconnect technology delivers breakthrough FPGA capacity, bandwidth, and power efficiency. Available at [http://www.xilinx.com/support/documentation/white\\_papers/wp380\\_Stacked\\_Silicon\\_Interconnect\\_Technology.pdf](http://www.xilinx.com/support/documentation/white_papers/wp380_Stacked_Silicon_Interconnect_Technology.pdf) (accessed December 31, 2013).

23 Ma, M. (2013) The expanding role of OSATS in the era of system integration. ConFab 2013, Las Vegas, NV.

24 Rahman, A. *et al.* (2013) Application requirements of system-in-package FPGAs. RTI 3D Architectures for Semiconductor Integration and Packaging Conference, Burlingame, CA, December 2013.